ISO9001:2015 quality management system controlled documents

# TX32M2300 Data Manual

珠海泰芯半导体有限公司 Zhuhai Taixin Semiconductor Co., Limited

珠海市高新区港湾一号科创园港 11 栋 3 楼

| 保密等级 | A          |                       | 文件编号 | TX-TX8C1260-RD |

|------|------------|-----------------------|------|----------------|

| 发行日期 | 2023-04-11 | TX32M2300 Data Manual | 文件版本 | V2. 2          |

## Revision Record

| Date       | Version | Description                                                                                       |

|------------|---------|---------------------------------------------------------------------------------------------------|

| 2023-04-11 | V2. 2   | 1. Modify the selection description of the positive and negative input in the comparator section; |

| 2023-02-03 | V2. 1   | 1. Solve the garbled code problem when some devices are opened for reading;                       |

| 2022-08-12 | V2. 0   | 1. Reformatted the document;                                                                      |

#### Notice:

- 1. The company reserves the right to the final interpretation of the function, performance, scheme, design and improvement of all the following products.

- 2. The Company reserves the right to copy and change the documents.

| 保密等级 | A          |                       | 文件编号 | TX-TX8C1260-RD |

|------|------------|-----------------------|------|----------------|

| 发行日期 | 2023-04-11 | TX32M2300 Data Manual | 文件版本 | V2. 2          |

2

珠海泰芯半导体有限公司 Zhuhai Taixin Semiconductor Co., Limited 珠海市高新区港湾一号科创园 港 11 栋 3 楼

## ${\tt Contents}$

| TX32M2300 Data Book                             | 1   |

|-------------------------------------------------|-----|

| 1 Master medium                                 | 1   |

| 1.1. Overview                                   | 1   |

| 1.2. Product features                           | 2   |

| 2. System and memory architecture               | 5   |

| 2.1. 32-bit RISC processor                      |     |

| 2.2. System architecture                        | 5   |

| 2.3. Memory mapping                             | 8   |

| 2.3.1. Bitband operation                        |     |

| 2.3.2. On-chip SRAM memory                      | 10  |

| 2.3.3. Overview of on-chip FLASH Memory         | 11  |

| 2.3.4. Boot configuration                       | 11  |

| 2.4. MCLR function                              | 11  |

| 3. Embedded flash memory                        |     |

| 3.1 Main features of flash memory               | 12  |

| 3.2. Flash memory function description          | 12  |

| 3.2.1. Structure of flash memory                | 12  |

| 3.2.2. Flash read protection                    | 13  |

| 3.2.3. Flash burn and erase operation           | 13  |

| 3. 3. Register                                  | 14  |

| 3. 3. 1. Register base address                  | 14  |

| 3. 3. 2. Register list                          | 14  |

| 3. 3. 3. Register details                       |     |

| 4. Interrupts and events                        | 22  |

| 4.1. Nested vector interrupt controllers        | 22  |

| 4.2. System tick (SysTick) calibration register | 22  |

| 4.3. Interrupt function description             | 22  |

| 4.4. External Interrupt/Event Controller (EXTI) | 24  |

| 4.4.1. Main features                            | 24  |

| 4.4.2. Wake event Management                    | 25  |

| 5. CRC Computing Unit                           | 107 |

| 5.1. Main features                              | 107 |

| 5.2. Registers                                  | 107 |

| 5. 2. 1. Register base address                  | 107 |

| 5. 2. 2. Register list                          | 107 |

|    | 5. 2. 3. Register details                               | 108 |

|----|---------------------------------------------------------|-----|

|    | 5.3. Operation flow                                     | 109 |

| 6. | power control                                           | 25  |

|    | 6.1. Power Supply                                       | 25  |

|    | 6.1.1. Voltage regulator                                |     |

|    | 6.2. Power Manager                                      |     |

|    | Ç                                                       |     |

|    | 6. 2. 1. Power-on Reset (POR) and Power-off Reset (PDR) |     |

|    | 6. 3. Low Power mode                                    |     |

|    | 6.4. Registers                                          |     |

|    |                                                         |     |

|    | 6. 4. 1. Register base address                          |     |

|    | 6. 4. 2. Register list                                  |     |

|    | 6. 4. 3. Register details                               |     |

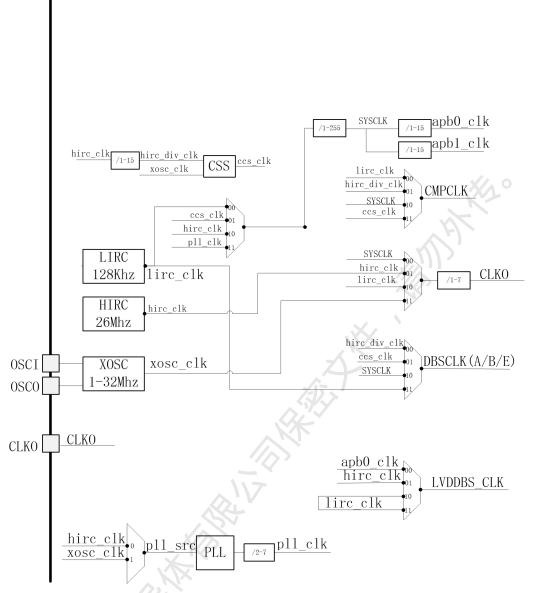

| 7. | Reset and clock control                                 | 30  |

|    | 7.1. Reset                                              |     |

|    | 7.1.1. The system resets                                | 30  |

|    | 7.2. Master reset                                       |     |

|    | 7.2.1. Power reset                                      |     |

|    | 7. 3. Clock                                             | 31  |

|    | 7.3.1. XOSC clock                                       | 31  |

|    | 7.3.2. HIRC clock                                       |     |

|    | 7. 3. 3. PLL                                            |     |

|    | 7.3.4. LIRC clock                                       |     |

|    | 7.3.5. System Clock (SYSCLK) selection.                 |     |

|    | 7.3.6. DBSCLK select                                    |     |

|    | 7.3.7. LVDDBS CLK clock Selection                       |     |

|    | 7.3.8. CMPCLK Clock Selection                           |     |

|    | 7.3.9. CMPCLK Clock Safety System (CSS)                 |     |

|    | 7.4. Registers                                          | 35  |

|    | 7.4.1. Register base address                            | 35  |

|    | 7. 4. 2. Register list                                  | 35  |

|    | 7.4.3. Register definition                              | 36  |

| 8. | GP10                                                    | 54  |

|    | 8.1. Main features of GPIO                              |     |

|    | 8.2. Function description of GPIO                       | 55  |

|    | 8.2.1. General Purpose IO (GPIO)                        |     |

|    | 8.2.2. Single bit operation                             |     |

|    | 8.2.3. Multiplexing function (AF)                       |     |

|    | 8.2.4. GPIO locking mechanism                           |     |

|    | o. 2. i. of to tooking meenantom                        | 51  |

|     | 8.2.5. Input configuration                    | . 57 |

|-----|-----------------------------------------------|------|

|     | 8.2.6. Output configuration                   | 58   |

|     | 8.2.7. Simulate input configuration           | 58   |

|     | 8.3. Registers                                | 59   |

|     | 8. 3. 1. Register base address                | 59   |

|     | 8. 3. 2. Register list                        |      |

|     | 8. 3. 3. Register definition in detail        | 61   |

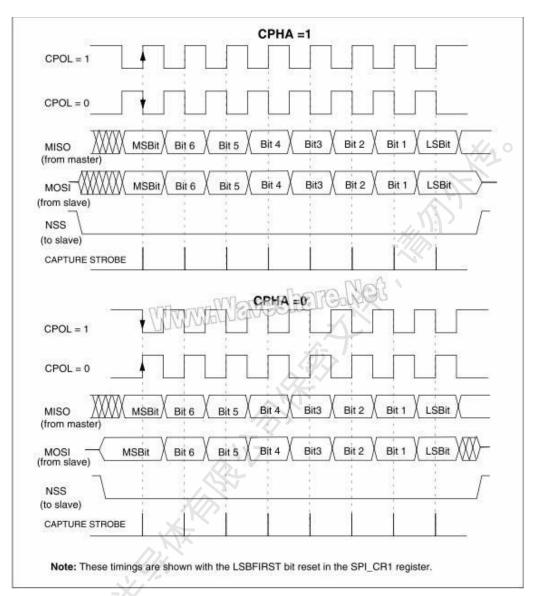

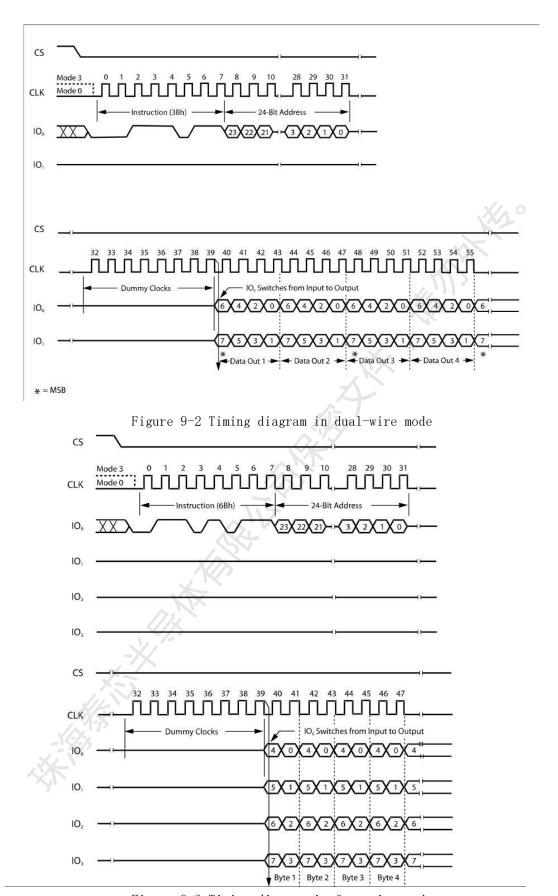

| 9.  | Communication interface peripheral CSI        | 77   |

|     | 9. 1. SPI_I2C                                 | 77   |

|     | 9.1.1. SPI function Description               | . 77 |

|     | 9.1.2. I2C function description               | . 78 |

|     | 9.1.3. SPI timing diagram.                    | . 79 |

|     | 9.1.4. IO MAPPING                             | 81   |

|     | 9. 2. Registers                               | 81   |

|     | 9. 2. 1. Register base address                | 81   |

|     | 9. 2. 2. Register list                        | 81   |

|     | 9. 2. 3. Register details                     | 82   |

|     | 9.2.4. Instructions for use                   |      |

| 10. |                                               |      |

|     | 10.1. Overview                                | 94   |

|     | 10. 2. Registers                              | 95   |

|     | 10. 2. 1. Register base address               | 95   |

|     | 10. 2. 2. Register list                       |      |

|     | 10. 2. 3. Register details                    | 96   |

|     | 10.2.4. Instructions for use                  | 105  |

| 11. | Hardware acceleration unit                    | 110  |

|     | 11.1. Introduction to the acceleration unit   | 110  |

|     | 11.2. Main features of hardware division      | 110  |

|     | 11.3. Hardware division function introduction | 111  |

|     | 3/14                                          |      |

|     | 11.4. Registers                               | 111  |

|     | 11.4.1. Register base address                 | 111  |

|     | 11.4.2. Register list                         |      |

|     | 11.4.3. Register details                      |      |

| 12. | Comparator (COMP)                             | 113  |

|     | 12.1. Introduction                            | 113  |

|     | 12.2. Key features                            | 113  |

|     | 12.3. Function Description                    | 114  |

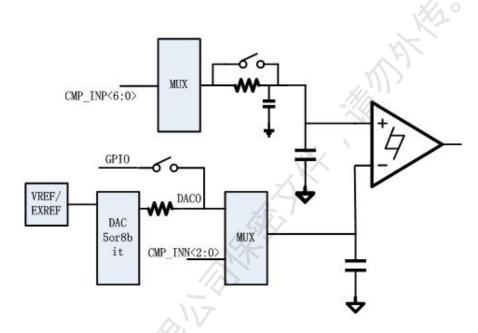

|     | 12.3.1. Comparator function block diagram     | 114  |

|     | 12.3.2. Comparator input and output                  | 115 |

|-----|------------------------------------------------------|-----|

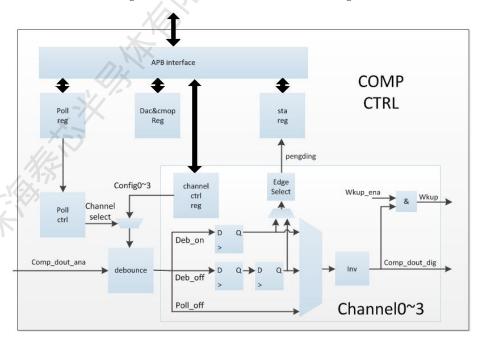

|     | 12.3.3. Comparator working mode                      | 115 |

|     | 12.3.4. Comparator filter control                    | 116 |

|     | 12.3.5. Comparator polling cycle                     | 116 |

|     | 12.3.6. Comparator interrupt and wake up             | 117 |

|     | 12.3.7. Comparator lock mechanism                    |     |

|     | 12.3.8. Comparator lag phenomenon                    | 117 |

|     | 12.4. Registers                                      | 118 |

|     | 12. 4. 1. Register base address                      |     |

|     | 12. 4. 2. Register list                              |     |

|     | 12. 4. 3. Register details                           |     |

| 13. |                                                      | 123 |

|     | 13.1. Introduction                                   |     |

|     | 13.2. Main features                                  | 123 |

|     |                                                      |     |

|     | 13.3. Register Trace                                 |     |

|     | 13. 3. 1. Register base address                      | 123 |

|     | 13. 3. 2. Register list                              | 123 |

| - 4 | 13.3.3. Register details                             |     |

| 14. | ADC                                                  | 126 |

|     | 14.1. Function brief                                 | 126 |

|     | 14.2. Main features                                  |     |

|     | 14.3. Structural block diagram                       | 127 |

|     |                                                      |     |

|     | 14.4. Function description                           | 128 |

|     | 14.4.1. ADC switch control                           | 128 |

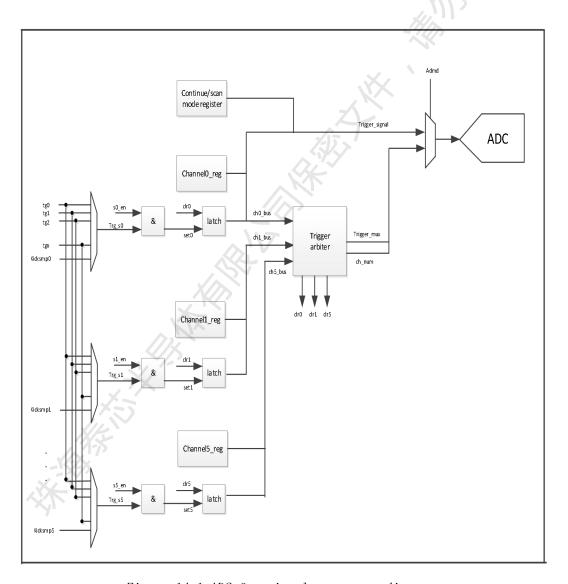

|     | 14.4.2. Channel selection                            | 128 |

|     | 14.4.3. ADC working mode                             |     |

|     | 14.4.4. DMA request                                  |     |

|     |                                                      | 130 |

|     | 14.4.6. Continuous sampling interval is configurable |     |

|     | 14.4.7. Externally triggered conversion              |     |

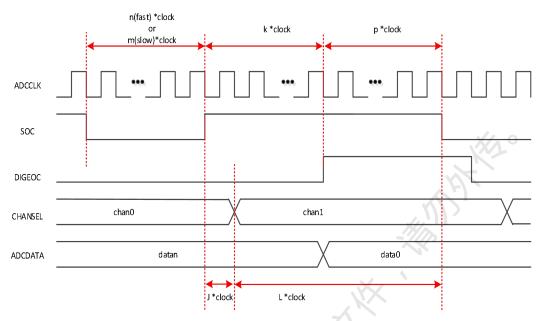

|     | 14.5. ADC interface timing                           | 131 |

|     | 14.5.1. ADC Power-on Sequence                        | 131 |

|     | 14.6. Register                                       | 132 |

|     | 14.6.1. Register base address                        | 132 |

|     | 14. 6. 2. Register list                              | 132 |

|     | 14. 6. 3. Register details                           | 133 |

|     |                                                      | 134 |

| 15. | Timer                                                | 143 |

|     | 15.1 Introduction                                    | 143 |

| 15. 2. Main features                                                   | . 143 |

|------------------------------------------------------------------------|-------|

| 15.3. Function description                                             | 144   |

| 15.3.1. Time base unit                                                 | 144   |

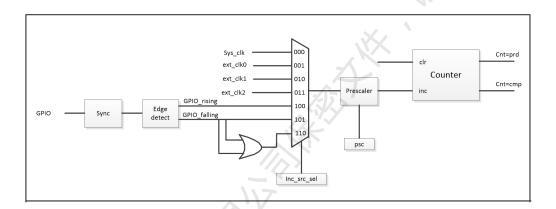

| 15.3.2. Count source selection                                         | 144   |

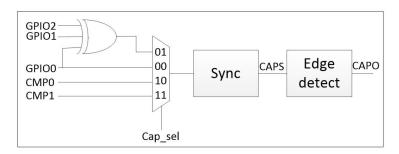

| 15.3.3. Enter the capture source                                       | 145   |

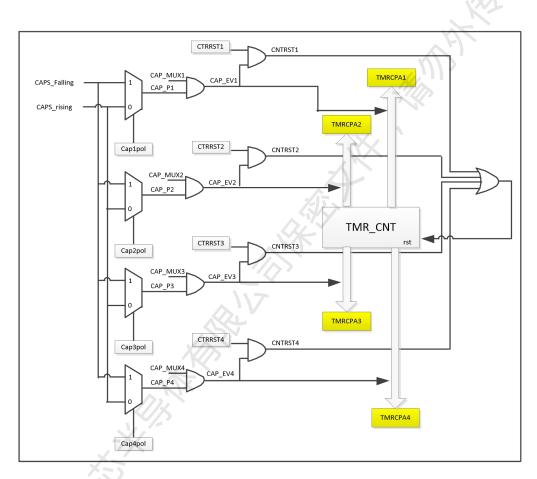

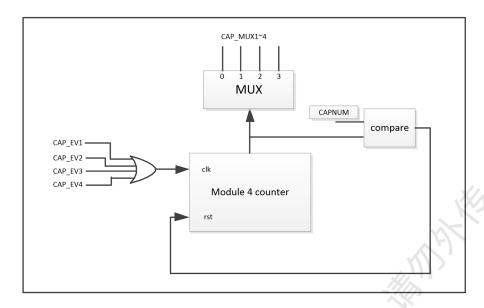

| 15.3.4. Enter the capture mode                                         |       |

| 15.3.5. PWM mode                                                       |       |

| 15.3.6. Trigger ADC sampling                                           | 149   |

| 15.3.7. timer synchronizes output                                      | . 149 |

| 15.3.8. Slave mode                                                     |       |

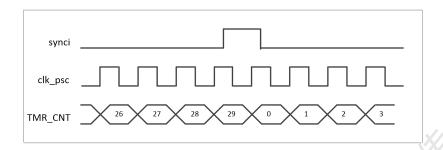

| 15.3.9. Reset Mode                                                     | . 149 |

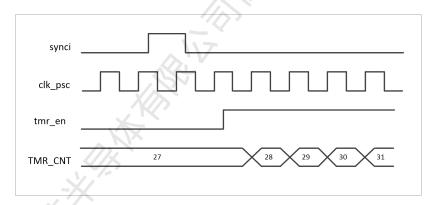

| 15.3.10. Trigger Mode                                                  |       |

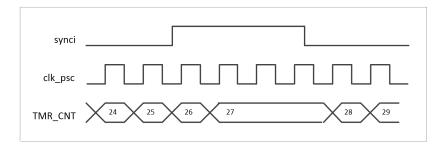

| 15.3.11. Gating mode                                                   |       |

| 15.3.12. DMA transfer mode                                             |       |

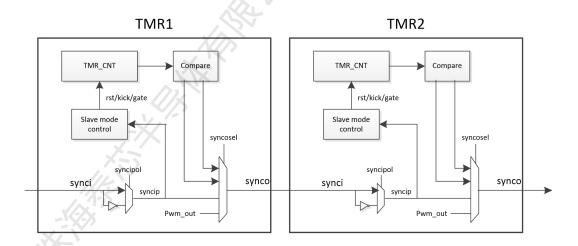

| 15.3.13. Cascading between multiple timers                             |       |

| 15.3.14. The value of multiple timers is cleared simultaneously        |       |

| 15.3.15. Generate PWM signal with carrier                              |       |

| 15. 3. 15. Register                                                    |       |

| 15. 4. 1. Register base address                                        |       |

| 15. 4. 2. Register list                                                |       |

| 15. 4. 3. Register details                                             | . 155 |

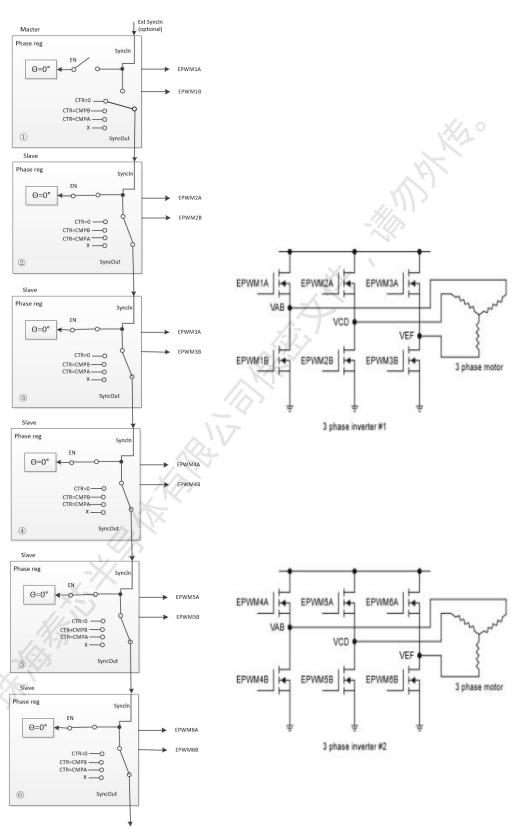

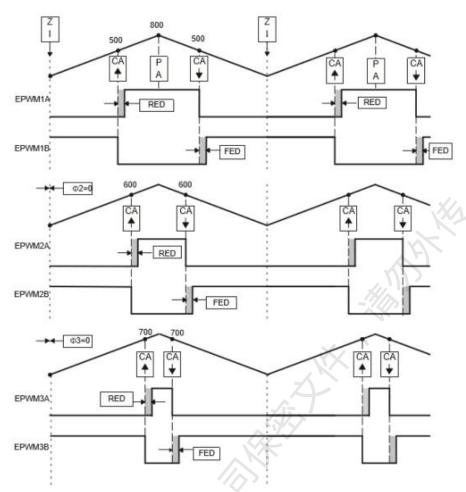

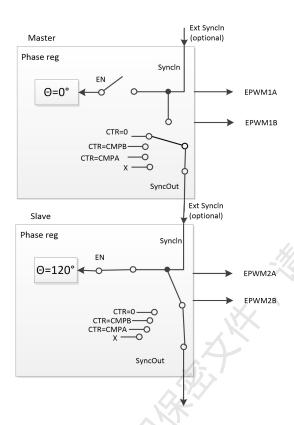

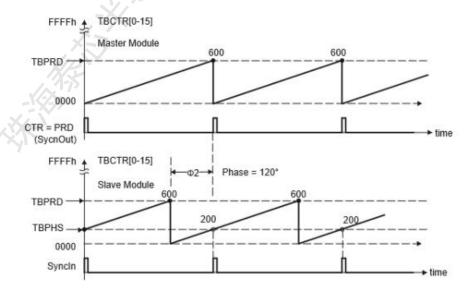

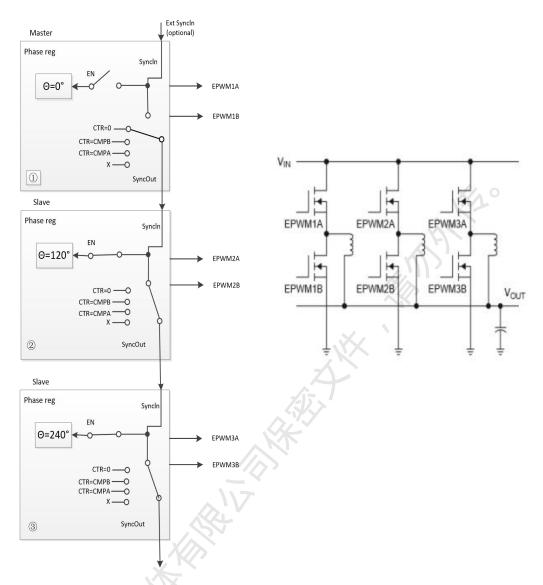

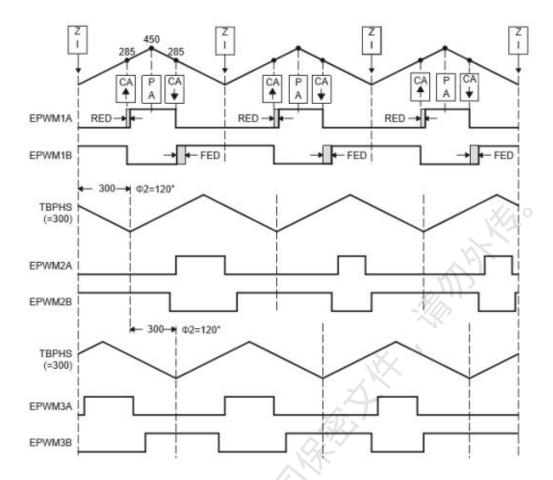

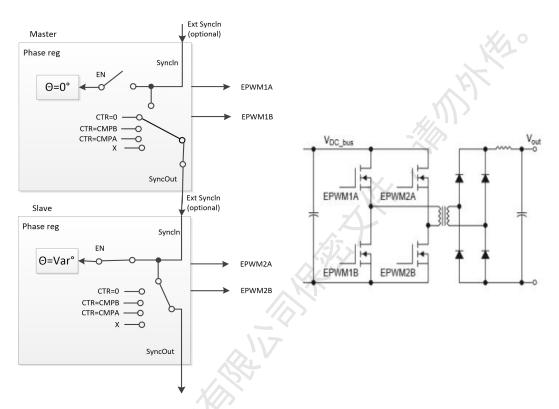

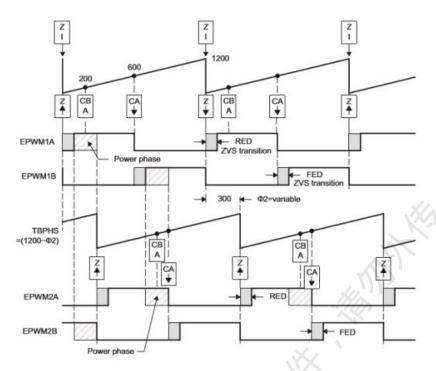

| EPWM.                                                                  |       |

| 16.1. Introduction                                                     | . 160 |

| 16.2. Introduction to the submodule                                    | . 161 |

| 16.2.1. Time base Counter Sub-module (Time-base)                       | 161   |

| 16.2.2. Time Base Counter comparator Submodule                         |       |

| 16.2.3. Action-qualifier submodule                                     | . 162 |

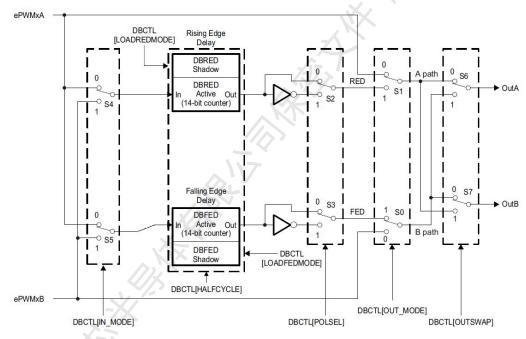

| 16.2.4. Dead-band submodule (dead-band)                                | 163   |

| 16.2.5. Event-trigger Submodule                                        |       |

| 16.2.6. Fault Zone Submodule (Trip-zone)                               |       |

| 16. 3. Function description and common topologies                      |       |

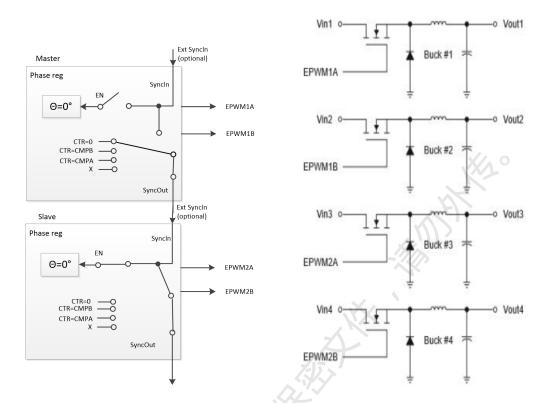

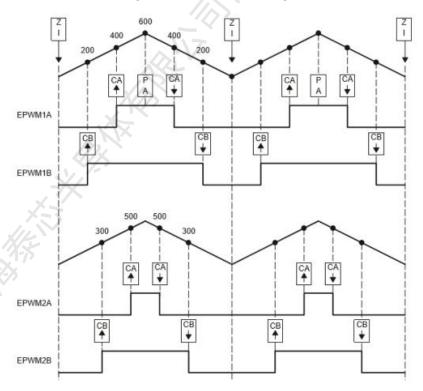

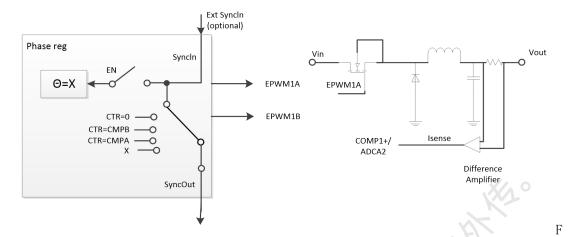

| 16.3.1. Independent frequency control of multiple Buck converter cir   |       |

| re. C. 1. Independent frequency control of martiple back converter eff |       |

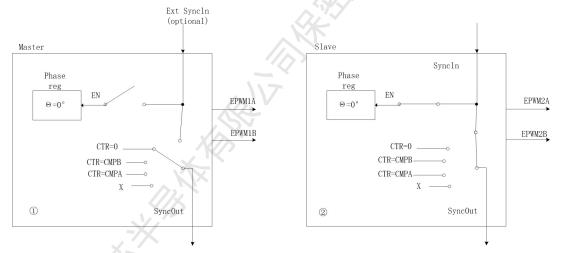

| 16.3.2. Control multiple Buck converter circuits at the same freque    |       |

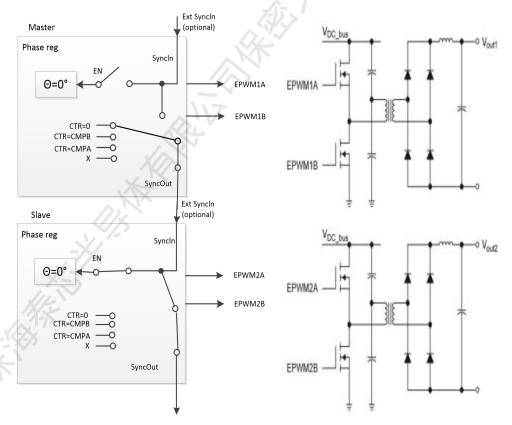

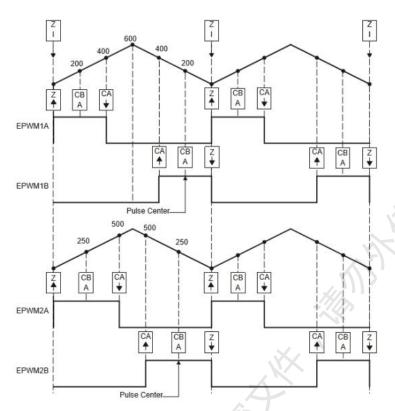

| 16.3.3. Control multiple H Half bridge circuit (HHB) conversion cir    | -     |

| 10.0.0. Control marriple in harr bridge criteria (imb) conversion cri  |       |

| 16.3.4. Control of motor two-three-phase inverters (ACI and PMSM)      |       |

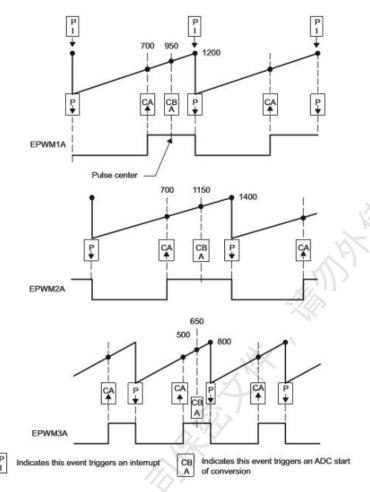

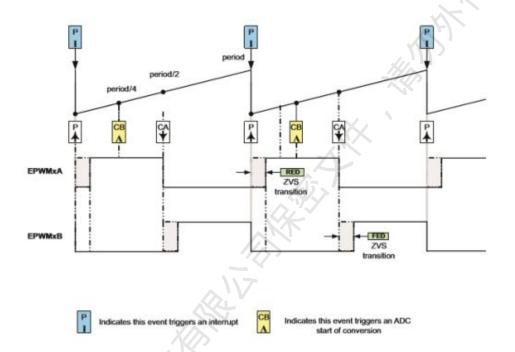

| 16.3.5. Practical application of phase control between PWM modules.    |       |

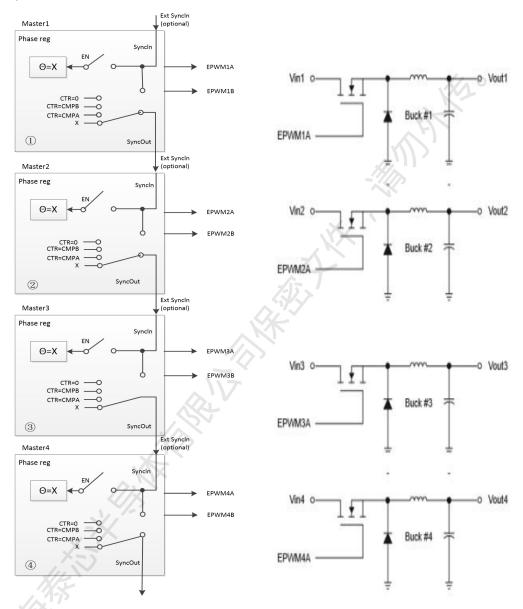

| 16.3.6. Control three-phase staggered DC/DC switching circuit          |       |

|                                                                        |       |

| 16.3.7. Full Bridge conversion circuit (ZVSFB) for control of 0 vo     | Itarr |

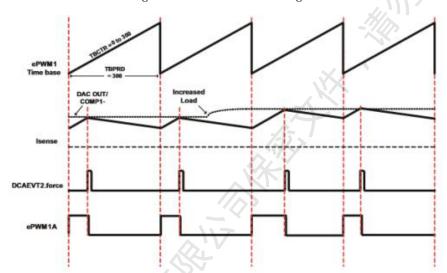

|     | 16.3.8. Controlling the Peak Current Mode (Peak Current Mode) Controls | the |

|-----|------------------------------------------------------------------------|-----|

|     | Buck module                                                            | 178 |

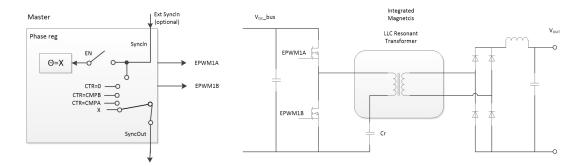

|     | 16.3.9. Control H-bridge LLC resonant converter                        | 179 |

|     | 16.4. Register                                                         | 180 |

|     | 16. 4. 1. Register base address                                        | 180 |

|     | 16. 4. 2. Register list                                                | 180 |

|     | 16. 4. 3. Register details                                             | 181 |

| 17. | WDT                                                                    | 206 |

|     | 17.1. Introduction                                                     | 206 |

|     | 17. 2. Register                                                        |     |

|     | 17. 2. 1. Register base address                                        | 207 |

|     | 17. 2. 2. Register list                                                | 207 |

|     | 17 2 3 Register details                                                | 207 |

## 1. Master directory

## 1.1. Overview

This product uses a high-performance 32-bit microcontroller with a maximum operating frequency of 72MHz, built-in 32KB high-speed Flash memory, 6KB SRAM, rich enhanced I/O ports and peripherals to connect to the external bus. This product contains 1 12-bit ADC, 1 8-bit precision DAC, 1 multi-function comparator, 3 operational amplifiers, 1 16-bit advanced timer, 5 16-bit general purpose timers, 1 32-bit general purpose timer, 1 Watchdog timer, 1 System tick timer. Also includes the standard communication interface: 2 SPI/IIC interface and 2 UART interface, among which UARTO can realize the code upgrade from any pin, built-in a 32 bit division 16 unsigned divider.

The operating voltage of this product series is  $2.0V^5$ 5.5V, and the operating temperature range is  $-40 \, ^{\circ}$ C  $^{\circ}$ 105  $^{\circ}$ C. A variety of power saving operating modes ensure the requirements of low power applications.

The product is available in four packages, including LQFP32, SSOP28, SSOP24 and TSSOP20. The peripherals in the device are configured differently depending on the package form.

A basic introduction to all peripherals in this family is given below.

These rich peripheral configurations make this product microcontroller suitable for a variety of applications:

- Fan, fan, etc

- Consumer Electronics

- Smart home

- Motor drives and application controls

- Medical and handheld devices

- Industrial Controls

- Industrial applications: Programmable controllers (PLCS), frequency converters, printers and scanners

## 1.2. Product Features

## > Kernel and System

- 32-Bit RISC architecture CPU

- Maximum working frequency: 72MHz

- Single cycle 32-bit multiplication instruction

- 32 interrupt sources, configurable 4-layer interrupt priority, support interrupt entry address Remap

- Supports bitband operation

- Support double pin debugging interface

#### > Memory

- 32K Byte Flash program memory (NO EEPROM Flash), Sector erase 20,000 times

- Internal 6K Byte SRAM

- Boot Loader supports on-chip Flash, supports single/dual pin UART Online

User Programming (IAP)/Online System Programming (ISP)

## > Clock, reset, and power management

- 2V to 5.5V power supply

- Power on/power off reset (POR/PDR), Programmable Voltage Monitor (PVD)

- External 1-32MHz crystal oscillator

- Factory-tuned 26MHz (+/ -1.5%) high speed oscillator embedded

- Embedded 128KHz low speed oscillator

- PLL outputs 72MHz clock

- Built-in Clock Security System (CSS)

- WDT reset

## > DMA support

- Supported peripherals: EFLASH, UART, SPI/I2C, CRC, TIMER, ADC

#### ➢ GPIO

- Supports up to 30 GPIOs

- All I/O ports can trigger edge or level response interrupts to wake up low power mode

- All ports can input and output 5V signals

- Support for key detection

## > Communication interface peripherals

- 2 SPI high-speed serial interface, Master under the maximum support system clock frequency half transmission, support 1/2/4 line master-slave mode, support I2C mode

- 2 UART interface, support RS232/RS485 protocol, UARTO can support any IO program upgrade

#### > Timer

- 1 16-bit advanced timer that supports 4 pairs of complementary outputs or

8 independent PWM outputs, supports dead zone insertion and event brake functions, and supports monopulse mode

- 5 16-bit universal timers, 1 32-bit timer, each with capture function

- 1 watchdog timer

- 1 system tick timer

#### Hardware acceleration unit

- Hardware signed divider (32bit/16bit)

#### > High security

- Support 5/7/8/16/32 bit CRC validation to ensure data accuracy

- Support code scrambling and hardware encryption and decryption

## ➤ Low power consumption

- Supports IDLE, STOP, and SLEEP low-power modes

- Static power consumption <20uA@25 ° C

- Low power wake-up time 10us fastest

## > 1 12-bit high speed analog-to-digital converter

- Supports up to 1.2Mhz sampling rate

- Up to 10 input channels

## > 1 comparator

- Supports 7 positive end inputs and 3 negative end inputs

- Support hardware channel polling

## > 3 operational amPs

- An op-amp in the same direction

- Built-in 4/6/8/10/12x gain available

- Closed-loop gain bandwidth optional

#### ➤ Built-in temperature sensor

#### ➤ High reliability

- ESD HBM 8KV

- EFT ±4500V

- Latch-up  $\pm 100$ mA @105°C

## > 96-bit chip Unique ID (UID)

### Package

- Die Form

- LQFP32/SSOP28/SSOP24/TSSOP20

## > Industrial grade temperature range

- -40°C <sup>∼</sup> 105°C

#### > Apply

- Fan, etc.

- Motor drive and application control

- Medical and handheld devices

- PC gaming peripherals and GPS platforms

- Industrial applications: Programmable controllers (PLCS), frequency converters, printers and scanners

- Alarm systems, video intercom, and heating ventilation and air conditioning systems

# 2. System and memory architecture

TX32M2300 series devices are based on RISC processor 32-bit general purpose microcontroller memory organization using Harvard structure, pre-defined memory mapping and up to 4 GB of storage space, fully ensure the flexibility and scalability of the system.

## 2.1. 32 bit RISC processor

The 32-bit RISC processor used in the TX32M2300 series is a 32-bit processor with low interrupt latency and low cost debugging features. The high integration and enhanced features make this RISC processor suitable for those market segments that require high performance and low power microcontrollers.

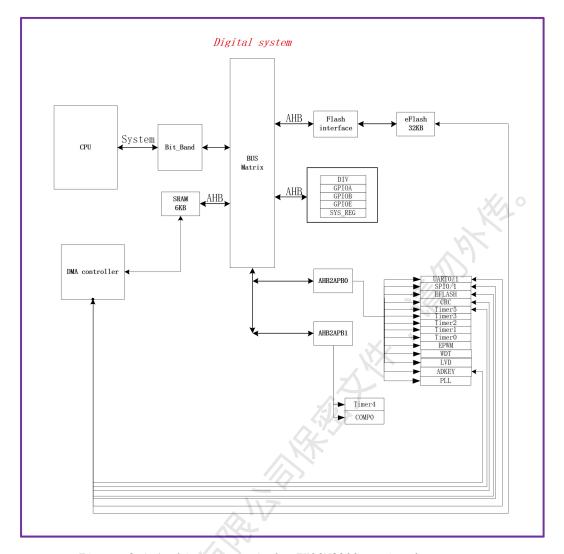

# 2.2. System Architecture

The TX32M2300 series devices adopt a 32-bit multi-layer bus structure, which makes parallel communication between multiple hosts and slaves in the system possible. The multi-layer bus architecture consists of an AHB interconnection matrix,

two AHB buses and two APB buses. The interconnection of the AHB interconnection matrix is described next. In the interconnection list of the system master/slave interconnection matrix, "1" indicates that the corresponding host can access the corresponding slave through the AHB interconnection matrix. Blank cells indicate that the corresponding host cannot access the corresponding slave through the AHB interconnection matrix.

The TX32M2300 series master system consists of the following parts:

- Two drive units:

- CPU core system Bus (S-bus)

- DMA controller

- Three passive units

- Internal flash memory

- Internal SRAM

- Bridge from AHB to APB (AHB2APBO/1), which connects all the APB devices

Figure 2-1 Architecture of the TX32M2300 series bus system

#### System Bus

This bus connects the CPU core's system bus (peripheral bus) to the bus matrix, which coordinates access between the core and various high-speed components.

#### DMA controller

This bus connects the CPU and peripheral modules to compete for access, coordinates access priorities, arbitrates, etc.

Table 2-1 Priority arrangement used by DMA module

| Modules | Priority | Instructions |

|---------|----------|--------------|

| CPU     | 0        | Highest      |

| SPI0    | 1        |              |

| SPI1    | 2        |              |

| UARTO   | 3        |              |

| ADC     | 4        |              |

| UART1  | 5 |         |

|--------|---|---------|

| CRC    | 6 |         |

| TIMER5 | 7 |         |

| Eflash | 8 | Minimum |

#### BusMatrix (BusMatrix)

The bus matrix manages the access arbitration between the kernel system bus and each peripheral module. The bus matrix consists of the master module bus and the slave module bus. AHB peripherals are connected to the system bus through the bus matrix.

#### AHB to APB bridge (AHB2APB bridge-APB)

The AHB to APB bridge provides a synchronous connection between the AHB and APB buses.

Note: When an 8-bit or 16-bit access is made to an APB register, the access is automatically converted to 32-bit access: the bridge automatically expands the 16 - or 8-bit data to match the 32-bit width.

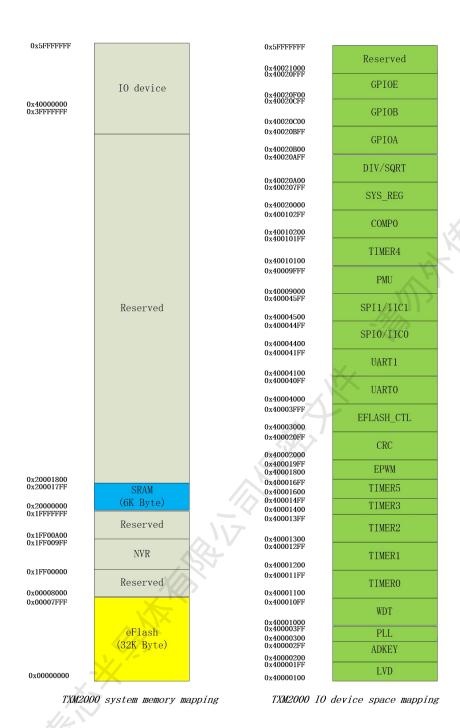

# 2.3. Memory Mapping

This 32-bit RISC processor uses the same set of buses to read instructions and load/store data. Both instruction code and data are located in the same memory address space, but in different address ranges. Program memory, data memory, registers, and I/O ports all reside in the same linear 4 GB address space. This is the maximum address range for 32-bit RISC, as its address bus width is 32 bits. Also, in order to reduce software complexity for different customers in the same application, the storage map is pre-defined according to the rules provided by the 32-bit RISC processor. In the memory mapping table, a portion of the address space is occupied by 32-bit RISC system peripherals and cannot be changed. In addition, the rest of the address space can be defined by the chip vendor.

The Memory mapping table of the TX32M2300 series device shows the memory mapping of the TX32M2300 series device, including code, SRAM, peripherals, and other pre-defined areas. Simplifies the address decoding of each peripheral.

Figure 2-2 Memory mapping table of TX32M2300 series

## 2.3.1. Bitband operation

To reduce the number of read-change-write operations, 32-bit RISC processors provide a bitband function that can perform single-atom bit operations. The memory map contains two areas that support bitband operations. One is the minimum 1MB range of the SRAM area, and the second is the minimum 1MB range of the on-chip and off-chip

areas. The addresses in these two zones have their own "bitband alias zone" in addition to normal applications. The bitband alias area expands each bit into a 32-bit word. When the user accesses the bitband aliasing area, the purpose of accessing the original bit is achieved.

The following formula shows how each word in the bitband alias area corresponds to the corresponding bit or destination bit in the bitband alias area.

bit\_word\_addr =bit\_band\_base +(byte\_offset×32)+(bit\_number×4) (Equation 31)

Where:

- bit\_word\_addr refers to the address of the bitband area target bit corresponding to the bitband alias area;

- bit\_band\_base refers to the start address of the bitband alias area;

- byte\_offset refers to the byte address offset of the byte in which the target bit of the bitband is located;

- bit\_number refers to the location of the target bit in the corresponding byte (0-7).

For example, to access the 7th bit of the address 0x2000 0200, the accessible bit-band alias area address is:

$bit_{word_addr} = 0x2200\ 0000 + (0x200 * 32) + (7 * 4) = 0x2200\ 401C$  (Formula 32)

If you write to  $0x2200 \ 401C$ , the 7th bit of  $0x2000 \ 0200 \ will$  change accordingly; If a read is done to  $0x2200 \ 401C$ , then  $0x01 \ or \ 0x00$  is returned as the 7th bit state of  $0x2000 \ 0200$ .

## 2.3.2. On-chip SRAM memory

The TX32M2300 series has built-in static SRAM up to 6K bytes. It can be accessed in bytes (8 bits), half words (16 bits), or words (32 bits). The SRAM starts at 0x2000 0000. Up to 6K bytes of SRAM on the data bus. Can be accessed by CPU or DMA using the fastest system clock without inserting any waits. DMA supports access with timer5, ADC, CRC, SPIO/1, UARTO/1, EFLASH.

## 2.3.3. Overview of on-chip FLASH memory

Flash memory has two different storage areas:

- The main flash storage block, which includes application and user data areas

(if needed)

- Information block, which consists of two parts:

- Option bytes Contains hardware and storage protection user configuration options.

- System memory contains the Boot loader code. See section on Built-in Flash Memory.

The flash memory interface executes instructions and data access based on the AHB protocol. The function of prefetch buffering can accelerate the speed of CPU code execution.

## 2.3.4. Boot Configuration

After the chip is reset, through the customer's own configuration in the main flash storage block, the boot mode pin can be selected as PC6 or PC0, and the default operation is pull-up or pull-down. After the boot delay, the CPU takes the address at the top of the stack from address  $0x0000\ 0000$  and executes the code from the address indicated by  $0x0000\ 0004$  of the boot memory.

The embedded bootstrap program is stored in the system memory and written by the manufacturer at production time. The program can be reprogrammed to the flash memory via UARTO.

#### 2.4. MCLR features

The TX32M2300 series supports the MCLR reset function by default. MCLR means that the input of a low level on a specific IO pin lasting more than 1.7ms causes the system to reset, as if it were reset after a power-on. When the MCLR function is disabled by the user using the user-defined bit in eflash. PE2 becomes the normal I/O function. Refer to the description of user-defined areas in Flash memory for details.

# 3. Embedded Flash Memory

## 3.1. Flash Memory Main Features

- 32K byte flash memory

- Memory structure:

- Main flash memory space: 32K bytes

- Secondary flash memory space (system memory) : 2K bytes

- Read interface with prefetch buffer

- Flash programming and erase operations

- Access and write protection

- Low power mode

# 3.2. Flash Memory Function Description

## 3.2.1. Flash Memory structure

The flash memory space consists of 32-bit wide storage units that can store both code and data. The main flash block is divided into 32 pages (1K bytes per page) with write protection set on a page basis (see storage protection related content).

| Modules                  | Name                  | Address                   | Size (bytes) |

|--------------------------|-----------------------|---------------------------|--------------|

|                          | Page 0                | 0x0000_0000 - 0x0000_03FF | 1K           |

|                          | Page 1                | 0x0000_0400 - 0x0000_07FF | 1K           |

| Marian Clark             | Page 2                | 0x0000_0800 - 0x0000_0BFF | 1K           |

| Main flash               | Page 3                | 0x0000_0C00 - 0x0000_0FFF | 1K           |

| memory space             | >X                    |                           | 1K           |

| >                        | Page 30               | 0x0000_7800 - 0x0000_7BFF | 1K           |

| 114                      | Page 31               | 0x0000_7C00 - 0x0000_7FFF | 1K           |

| 13                       | Sector 0              | 0x1FF0_0000 - 0x1FF0_01FF | 512          |

| -1(2)                    | Sector 1              | 0x1FF0_0200 - 0x1FF0_03FF | 512          |

| , XK-1                   | Sector 2              | 0x1FF0_0400 - 0x1FF0_057F | 384          |

| Sub-flash space          | User Parameters area  | 0x1FF0_0580 - 0x1FF0_06BF | 64           |

| Sub Trash space          | User profile area     | 0x1FF0_05C0 - 0x1FF0_05FF | 64           |

|                          | Chip information area | 0x1FF0_0600 - 0x1FF0_064F | 80           |

|                          | EOTP chip area        | 0x1FF0_0650 - 0x1FF0_068F | 64           |

|                          | EOTP User area        | 0x1FF0_0690 - 0x1FF0_06EF | 96           |

| Elech mediates           | CTRLRO                | 0x4000_3000 - 0x4000_3003 | 4            |

| Flash register interface | KST                   | 0x4000_3004 - 0x4000_3007 | 4            |

| interrace                | DONE                  | 0x4000_3008 - 0x4000_300B | 4            |

| PROG_ADDR     | 0x4000_3010 - 0x4000_3013 | 4 |

|---------------|---------------------------|---|

| PROG_DATA     | 0x4000_3018 - 0x4000_301B | 4 |

| ERASE_CTRL    | 0x4000_3020 - 0x4000_3023 | 4 |

| TIME_REGO     | 0x4000_3030 - 0x4000_3033 | 4 |

| TIME_REG1     | 0x4000_3034 - 0x4000_3037 | 4 |

| NVR_PASSWORD  | 0x4000_3050 - 0x4000_3053 | 4 |

| MAIN_PASSWORD | 0x4000_3054 - 0x4000_3057 | 4 |

| CRC_ADDR      | 0x4000_3058 - 0x4000_305B | 4 |

| CRC_LEN       | 0x4000_305C - 0x4000_305F | 4 |

| CRC_OUT       | 0x4000_3060 - 0x4000_3063 | 4 |

## 3.2.2. Flash read protection

The read operation can be completed in the entire product operating voltage range for storing instructions or data. Flash runs at the working frequency of 36MHz. If the working frequency is increased to more than 36MHz, the Flash reading sequence needs to perform frequency division.

The chip is equipped with cache buffer and prefetch buffer to improve the access efficiency of Flash.

If protection is enabled in the user configuration area, the Flash protection mechanism is automatically implemented when the SWD and other debugging interfaces are connected.

The read operation is completed by the following two registers:

- ① Configuration register (CTRLRO)

- 2 Timing 0 register (TIME REGO)

## 3.2.3. Flash burn and erase operations

Write and erase operations can be done over the entire product operating voltage range.

The burn and erase operation is completed by the following 6 registers, first configure the burn time sequence (TIME\_REG1) according to the burn clock, then configure the burn password, configure the programming address, and finally configure the programming data, you can start to execute the burn, and then wait for the end of the burn.

As long as the CPU does not access the Flash space, or has a cache hit when accessing Flash, the ongoing Flash write operation will not hinder the operation

of the CPU. In other words, while writing/erasing the Flash, any access to the Flash will cause the bus to stop until the write/erasing operation is complete, which means that the Flash can not be written/erasing at the same time, it can not get fingers and access data

# 3. 3. Registers

# 3. 3. 1. Register base address

| Name   | Base Address | Description            |

|--------|--------------|------------------------|

| Eflash | 0x40003000   | Base address of Eflash |

# 3. 3. 2. Register list

| Offset Address | Name                | Description                                |

|----------------|---------------------|--------------------------------------------|

| 0x0            | EFLASH_CTRLRO       | Control register                           |

| 0x04           | EFLASH_KST          | Trigger register                           |

| 0x08           | EFLASH_DONE         | Status register                            |

| 0x10           | EFLASH_PROGADDR     | Programming address register               |

| 0x18           | EFLASH_PROGDATA     | Programming data register                  |

| 0x20           | EFLASH_ERASECTRL    | Erasing the control register               |

| 0x24           | EFLASH_INTFERASEENA | Interrupt interrupts EFlash working status |

| 0x30           | EFLASH_TIMEREGO     | Timing O configures register               |

| 0x34           | EFLASH_TIMEREG1     | Timing 1 Configure registers               |

| 0x50           | EFLASH_NVRPASSWORD  | NVR area secret key register               |

| 0x54           | EFLASH_MAINPASSWORD | Main area key register                     |

| 0x58           | EFLASH_CRCADDR      | CRC address register                       |

| 0x5C           | EFLASH_CRCLEN       | CRC length register                        |

| 0x60           | EFLASH_CRCOUT       | CRC output Register                        |

# 3. 3. 3. Register Details

# 3. 3. 3. 1. EFLASH\_CTRLR0

| Bit(s) | Name                     | Description                                                                                                                                                                                                                                                           | R/W | Reset |

|--------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|

| 31:20  | Reserved                 |                                                                                                                                                                                                                                                                       | RO  | 0     |

|        |                          | The enable bit for an exception interrupt After the interrupt is enabled, the following exceptions are triggered:                                                                                                                                                     |     | 0     |

| 19     | Error Interrupt IE       | <ol> <li>Unaligned address programming</li> <li>Programming data error</li> <li>No write permission</li> <li>Erasing failed</li> </ol>                                                                                                                                | RW  | 0     |

| 18     | Normal Interrupt IE      | Normal interrupt enable bit for normal function  If the interrupt is enabled, the following conditions will trigger:  ① Programming ② Erase ③CRC check ④ Automatic programming                                                                                        | RW  | 0     |

| 17     | Reserved                 |                                                                                                                                                                                                                                                                       | RO  | 0     |

| 16     | Program<br>Clock select  | Eflash burns clock source selection. RC clock is recommended  0x0: High speed RC clock 2 frequency division  0x1: Crystal oscillator, only used if the RC is not on time                                                                                              | RW  | 0     |

| 15:12  | Reserved                 |                                                                                                                                                                                                                                                                       | RO  | 0     |

| 11     | LVD<br>Program Disable   | LVD power down burn control bit When LVD power off, whether to allow to interrupt eflash program and erase, generally when power off, immediately save important data in eflash, turn on this function, used to quickly let eflash in the idle state 0x0: Off 0x1: On | RW  | 0     |

| 10:6   | Reserved                 |                                                                                                                                                                                                                                                                       | RO  | 0     |

| 5      | Block<br>request Mode    | Request buffering mode for Program/Erase (for test use)  0x0: Off  0x1: On                                                                                                                                                                                            | RW  | 0     |

| 4      | Cache Write Back<br>Mode | Program/Sector Erase Write back to the cache automatically (Used for test) $0x0\colon \mbox{ Off } \\ 0x1\colon \mbox{ On }$                                                                                                                                          | RW  | 1     |

| 3 | Reserved        |                              | RO | 1 |

|---|-----------------|------------------------------|----|---|

| 2 | Prefetch Enable | Prefetch enable bit 0x0: Off | RW | 0 |

|   |                 | 0x1: On                      |    |   |

| 1 | Reserved        |                              | RO | 0 |

|   |                 | Cache enable bit             | DW |   |

| 0 | Cache Enable    | 0x0: 0ff                     | RW | 0 |

|   |                 | 0x1: 0n                      |    |   |

# 3. 3. 3. 2. EFLASH\_KST

| Bit(s) | Name                 | Description                                    | R/W  | Reset |

|--------|----------------------|------------------------------------------------|------|-------|

|        |                      | Eflash Error Clear Enable bit                  | 7    |       |

|        | EDIACII D. Cl.       | Note: Needs to be configured at the same time  |      |       |

| 31     | EFLASH Error Clear   | as BIT[15] to be valid                         | WO   | 0     |

|        | Enable               | 0x0: Off                                       |      |       |

|        |                      | 0x1: Open                                      |      |       |

|        |                      | Complete Status flag Clear enable bit          |      |       |

|        | DELIVER D. 1. CI     | Note: Needs to be configured at the same time  |      |       |

| 30     | EFLASH Pending Clear | as BIT[14] to be effective                     | WO   | 0     |

|        | Enable               | 0x0: Off                                       |      |       |

|        |                      | 0x1: On                                        |      |       |

| 29:27  | Reserved             |                                                | RO   | 0     |

| l      |                      | CRC kick enable bit                            |      |       |

|        |                      | Note: Needs to be configured at the same time  |      |       |

| 26     | CRC Kick Enable      | as BIT[10] to be effective                     | WO   | 0     |

|        | .)                   | 0x0: Off                                       |      |       |

|        |                      | 0x1: On                                        |      |       |

|        | />>                  | Auto program eflash Enable                     |      |       |

|        | A . D DDY ACT        | Note: Needs to be configured at the same time  |      |       |

| 25     | Auto Program EFLASH  | as BIT[9] to be effective                      | WO   | 0     |

|        | Enable               | 0x0: Off                                       |      |       |

|        |                      | Ox1: On                                        |      |       |

|        | XX                   | SRAM auto Program Enable bit                   |      |       |

|        | Valent Day           | Note: Needs to be configured at the same time  |      |       |

| 24     | Auto Program RAM     | as BIT[8] to be effective                      | WO   | 0     |

| 77     | Enable               | 0x0: Off                                       |      |       |

|        |                      | 0x1: On                                        |      |       |

| 23:21  | Reserved             |                                                | RO   | 0     |

|        |                      | Cache clear kick enable bit                    |      |       |

|        |                      | Note: It needs to be configured with BIT[4] to |      |       |

| 20     | Cache Clear Kick     | be valid                                       | WO   | 0     |

|        | Enable               | 0x0: Off                                       |      |       |

|        |                      | 0x1: Open                                      |      |       |

| 19:11  | Reserved             |                                                | RO   | 0     |

| 19.11  | neserveu             |                                                | I VO | Ι 0   |

| 15    | EFLASH Error Clear                | Exception flag clear bit Note: Needs to be configured at the same time as BIT[31] to be valid | WO   | 0 |

|-------|-----------------------------------|-----------------------------------------------------------------------------------------------|------|---|

|       |                                   | Write 1 Clear                                                                                 |      |   |

|       |                                   | Complete status flag clear bit                                                                |      |   |

| 14    | EFLASH Pending Clear              | Note: Needs to be configured at the same time                                                 | WO   | 0 |

| 14    | Erlash rending Clear              | as BIT[14] to be valid                                                                        | WO   | U |

|       |                                   | Write 1 Clear                                                                                 |      |   |

| 13:11 | Reserved                          |                                                                                               | RO   | 0 |

|       |                                   | CRC kick start                                                                                | .X// | 0 |

|       |                                   | Note: Needs to be configured at the same time                                                 |      |   |

| 10    | CRC Kick Start                    | as BIT[26] to be valid                                                                        | WO   | 0 |

|       |                                   | 0x0: Off                                                                                      | ( )  |   |

|       |                                   | 0x1: 0n                                                                                       | 7    |   |

|       |                                   | Auto-program trigger bits                                                                     |      |   |

|       | A . D DELACH                      | Note: Needs to be configured at the same time                                                 |      |   |

| 9     | Auto Program EFLASH<br>Kick start | as BIT[25] to be effective                                                                    | WO   | 0 |

|       |                                   | 0x0: Off                                                                                      |      |   |

|       |                                   | 0x1: On                                                                                       |      |   |

|       |                                   | SRAM automatically programs trigger bits                                                      |      |   |

|       | A + D DAME: 1                     | Note: Needs to be configured at the same time                                                 |      |   |

| 8     | Auto Program RAM Kick             | as BIT[24] to be effective                                                                    | WO   | 0 |

|       | start                             | 0x0: Off                                                                                      |      |   |

|       |                                   | 0x1: On                                                                                       |      |   |

| 7:5   | Reserved                          | 117                                                                                           | RO   | 0 |

|       |                                   | Cache clear bit                                                                               |      |   |

|       | Cache Clear Kick                  | Note: needs to be configured at the same time                                                 |      |   |

| 4     |                                   | as BIT[20] to be valid                                                                        | WO   | 0 |

|       | Start                             | 0x0: Off                                                                                      |      |   |

|       | />ı.                              | 0x1: On                                                                                       |      |   |

| 3:0   | Reserved                          |                                                                                               | RO   | 0 |

# 3. 3. 3. 3. EFLASH\_DONE

| Bit(s) | Name             | Description                             | R/W | Reset |

|--------|------------------|-----------------------------------------|-----|-------|

|        |                  | Error status flag bit                   |     |       |

| 31     | EFLASH Error     | 0x0: Normal                             | RO  | 0     |

|        |                  | 0x1: Abnormal                           |     |       |

| 30:20  | Reserved         |                                         | RO  | 0     |

|        |                  | Full chip erase abnormal status         |     |       |

| 19     | Chip Erase Error | 0x0: Works properly                     | RO  | 0     |

|        |                  | Ox1: Erase exception, error is valid    |     |       |

| 18     | Write permission | Programming permission exception status | RO  | 0     |

版权所有 侵权必究

|       | Error                 | 0x0: Working properly                     |      |   |

|-------|-----------------------|-------------------------------------------|------|---|

|       |                       | Ox1: No programming permissions, error is |      |   |

|       |                       | valid                                     |      |   |

|       |                       | Program address abnormal state            |      |   |

| 17    | Program Address       | OxO: Working properly                     | RO   | 0 |

|       | Error                 | Ox1: Unaligned address, error is valid    |      |   |

|       |                       | Abnormal state of programming data        |      |   |

|       |                       | Whether the programmed data is consistent |      |   |

| 16    | Program Data Error    | with the data configured by the software  | RO   | 0 |

|       |                       | 0x0: Works properly                       | X/,  | 0 |

|       |                       | Ox1: Data is inconsistent, error is valid |      |   |

|       |                       | Eflash working status flag                |      |   |

| 15    | EFLASH Busy           | 0x0: Idle status                          | RO   | 0 |

|       |                       | 0x1: In progress                          | >    |   |

| 14:11 | Reserved              | -7117                                     | RO   | 0 |

|       |                       | CRC DONE flag                             |      |   |

| 10    | CRC Done              | 0: In progress                            | RO   | 1 |

|       |                       | 1: Idle                                   |      |   |

|       |                       | Auto program eflash Done flag             |      |   |

| 9     | Auto Program EFLASH   | 0x0: Idle                                 | RO   | 0 |

|       | Done                  | 0x1: Finished                             |      |   |

|       |                       | Auto program RAM done flag                |      |   |

| 8     | Auto Program RAM Done | 0x0: Idle                                 | RO   | 0 |

|       |                       | 0x1: Finished                             |      |   |

| 7     | Reserved              | 117                                       | RO   | 0 |

|       |                       | Program end flag                          |      |   |

| 6     | Program Done          | 0x0: In progress                          | RO   | 1 |

|       | Trogram Done          | 0x1: Idle                                 | 11.0 | - |

| 5     | Reserved              |                                           | RO   | 0 |

| -     | A1                    | Cache initialization flag                 |      | - |

| 4     | Cache Clear Done      | 0x0: In progress                          | RO   | 1 |

|       |                       | 0x1: Idle                                 | 11.0 | - |

| 3:2   | Reserved              |                                           | RO   | 0 |

|       |                       | The Main field completely erases the flag |      | - |

| 1     | Chip Erase Done       | 0x0: Running                              | RO   | 1 |

|       | 1/2×17p               | 0x1: Idle                                 |      |   |

|       |                       | Sector (512 byte) Erase flag              |      |   |

| 0     | Sector Erase Done     | 0x1: Running                              | RO   | 1 |

|       | Diago Dollo           | 0x0: Idle                                 | 1.0  | _ |

|       |                       | 0.10. 2.010                               | I    |   |

# 3. 3. 4. EFLASH\_PROGADDR

| Bit(s) | Name         | Description                              | R/W | Reset |

|--------|--------------|------------------------------------------|-----|-------|

| 21.20  | D            | Bit width Settings for programming       | DW  |       |

| 31:30  | Program Byte | eflash is divided into code area and RAM | RW  | _     |

|      |                    | area through the DATA RAM setting of the   |    |   |

|------|--------------------|--------------------------------------------|----|---|

|      |                    | functional area, where the RAM area can    |    |   |

|      |                    | perform 1/2/4 byte programming, while the  |    |   |

|      |                    | code area can only perform 4 byte          |    |   |

|      |                    | programming                                |    |   |

|      |                    | 0x0:1 byte                                 |    |   |

|      |                    | 0x1:2 byte                                 |    |   |

|      |                    | 0x2:4 byte                                 |    |   |

|      |                    | The address of the program is NVR zone or  |    |   |

| 29   | David and MVD C. I | not                                        | DW | 0 |

| 29   | Program NVR Select | 0x0: MAIN area                             | KW | _ |

|      |                    | 0x1: NVR area                              |    |   |

|      |                    | Address for eflash programming             | 7) |   |

|      | Program Address    | In automatic programming mode, as the      | 7  |   |

|      |                    | destination address:                       |    |   |

|      |                    | In auto-programmed RAM mode, this address  |    |   |

|      |                    | serves as the RAM address;                 |    |   |

|      |                    | In auto-programmed EFLASH mode, this       |    |   |

|      |                    | address acts as the EFLASH address.        |    |   |

|      |                    | To program in the code field:              |    |   |

| 28:0 |                    | Only 4 byte programming is supported       | RW | _ |

|      |                    | Programming in the DATARAM area:           |    |   |

|      |                    | The programming address is half word       |    |   |

|      |                    | aligned and supports 1/2 byte programming  |    |   |

|      |                    | The programming address is aligned in word |    |   |

|      |                    | and supports 1/2/4 byte programming        |    |   |

|      |                    | Programming addresses are odd and only 1   |    |   |

|      |                    | byte programming is supported              |    |   |

# 3. 3. 3. 5. EFLASH\_PROGDATA

| Bit(s) | Name         | Description                                | R/W | Reset |

|--------|--------------|--------------------------------------------|-----|-------|

| 31:0   | D D.         | eflash programming data, need to configure | DW  | 0     |

| 31.0   | Program Data | the address can be carried out             | I/W | 0     |

# 3. 3. 3. 6. EFLASH\_ERASECTRL

| Bit(s) | Name                    | Description                                 | R/W | Reset |

|--------|-------------------------|---------------------------------------------|-----|-------|

|        |                         | Trigger of Chip erase full                  |     |       |

| 31     | Chip Erase Kick Start   | Write "1" trigger, you need to configure    | RO  | 0     |

|        |                         | the password first                          |     |       |

|        |                         | Trigger of Sector erase                     |     |       |

| 30     | Sector Erase Kick Start | Write "1" to trigger, you need to configure | RO  | 0     |

|        |                         | the password first                          |     |       |

|      |                      | The sector enable bit of the NVR    |    |   |

|------|----------------------|-------------------------------------|----|---|

| 29   | NVR Sector Enable    | 0: The MAIN area                    | RW | 0 |

|      |                      | 1: NVR area                         |    |   |

| 28:7 | Reserved             |                                     | RO | 0 |

| 6:0  | Erase Sector Address | Erase sector selection, range 0-127 | RW | 0 |

## 3. 3. 3. 7. EFLASH\_TIMEREGO

| Bit(s) | Name     | Description                                                      | R/W | Reset |

|--------|----------|------------------------------------------------------------------|-----|-------|

| 31:20  | Reserved |                                                                  | RO  | 0     |

| 19:16  | PGH      | WEb low to PROG2 high hold min time is 15ns                      | RW  | 1     |

| 15:12  | ADS      | BYTE/Address/data setup min time is 15ns                         | RW  | 1     |

| 11:8   | ADH      | BYTE/Address/data hold min time is 15ns                          | RW  | 1     |

| 7:4    | RW       | Latency to next operation after PROG/ERASE low min time is 100ns | RW  | 8     |

| 3:0    | RC       | Read Cycle Min Time is 25/30ns                                   | RW  | 0     |

## 3. 3. 3. 8. EFLASH\_TIME\_REG1

| Bit(s) | Name     | Description                              | R/W | Reset |

|--------|----------|------------------------------------------|-----|-------|

| 31:20  | Reserved |                                          | RO  | 0     |

| 18:8   | 1ms unit | lms time configuration value, in lus     | RW  | 1000  |

| 7:0    | lus unit | lus time configuration value, the system | RW  | 26    |

|        |          | default is 26MHz                         |     |       |

# 3.3.3.9. EFLASH\_NVR\_PASSWORD

| Bit(s) | Name         | Description                                                                            | R/W | Reset |

|--------|--------------|----------------------------------------------------------------------------------------|-----|-------|

| 31:10  | NVR password | The password is 0x20150931 and NVR can only be erased and programmed once the password | RW  | 0     |

|        | . 7.5        | is opened                                                                              |     |       |

# 3. 3. 10. EFLASH\_MAIN\_PASSWORD

| Bit(s) | Name          | Description                               | R/W | Reset |

|--------|---------------|-------------------------------------------|-----|-------|

|        |               | The password is 0x20170230, and you can   |     |       |

| 31:10  | Main password | only erase and program Main once you open | RW  | 0     |

|        |               | the password                              |     |       |

## 3. 3. 3. 11. EFLASH\_CRC\_ADDR

| Bit(s) | Name        | Description                               | R/W | Reset |

|--------|-------------|-------------------------------------------|-----|-------|

| 31:30  | Reserved    |                                           | RO  | 0     |

|        |             | Address is NVR zone                       |     |       |

| 29     | NVR Select  | 0x0: The MAIN zone                        | RW  | 0     |

|        |             | 0x1: NVR area                             |     |       |

|        |             | The start address of the CRC DMA, as the  |     |       |

|        |             | source address                            |     |       |

| 28:2   | DMA Address | In auto-programmed RAM mode, this address |     | 8     |

| 20:2   | DMA Address | serves as the EFLASH address;             | RW  | U     |

|        |             | In auto-programmed EFLASH mode, this      | 70  |       |

|        |             | address serves as the RAM address.        |     |       |

| 1:0    | Reserved    | Reserved, lower 2-bit address fixed to 0, | DO. | 0     |

| 1:0    | reserved    | word aligned                              | RO  | U     |

## 3. 3. 3. 12. EFLASH\_CRC\_LEN

| Bit(s) | Name       | Description                               | R/W | Reset |

|--------|------------|-------------------------------------------|-----|-------|

| 31:2   | DMA length | The length of the CRC DMA                 | RW  | 0     |

| 1:0    | Reserved   | Reserved, lower 2-bit address fixed to 0, | RO  | 0     |

|        |            | word aligned                              |     |       |

# 3. 3. 3. 13. EFLASH\_CRC\_OUT

| Bit(s) | Name         | Description                                 | R/W | Reset |

|--------|--------------|---------------------------------------------|-----|-------|

|        | . <b>*</b>   | CRC Result Output                           |     |       |

|        |              | Polynomial CRC-32 is as follows, the result |     |       |

|        | (//s`        | of the inverse is the official result, CRC  |     |       |

| 31:00  | O CRC Result | written to EFLASH needs the official value  | RO  | 0     |

|        | 7//          | to take the inverse representation!!        |     |       |

|        | X.57         | x32+x26+x23+x22+x16+x12+x11+x10+x8+x7+x5    |     |       |

|        | XX           | +x4+x2+x+1                                  |     |       |

## 4. Interrupts and events

## 4.1. Nested vector interrupt controller

Basic functions:

- All interrupts can be masked (except NMI)

- 16 programmable priority levels (4-bit interrupt priority is used)

- Low latency exception and interrupt handling

- Power management Controls

- Implementation of system control register

The interface of nested vector interrupt controller (NVIC) and processor core is closely connected, which can realize low latency interrupt processing and efficiently deal with late interrupts.

The nested vector interrupt controller manages interrupts, including kernel exceptions. Refer to the CPU Technical Reference Manual for more instructions on exceptions and NVIC programming.

# 4.2. System Tick (SysTick) calibration value register

This chip does not support using an external clock to time 1ms.

# 4.3. Interrupt Function Description

The processor and the nested vector Interrupt Controller (NVIC) prioritize and handle all exceptions in Handler mode. When an exception occurs, the system automatically stacks the current working state of the processor, and automatically unstacks it after executing the Interrupt service subroutine (ISR).

The orientation is carried out in parallel with the current working state, thus improving the interrupt entry efficiency. The processor supports tail-biting interrupts, which can realize back-to-back interrupts, greatly reducing the

overhead caused by repeated switching of working states. The NVIC Exception types list all the exception types.

Table 4-1 NVIC exception types in the CPU

| Types of exceptions | Vector<br>number | Priority | Vector address            | Description                                               |

|---------------------|------------------|----------|---------------------------|-----------------------------------------------------------|

| _                   | 0                | _        | 0x00000000                | Retain                                                    |

| Reset               | 1                | - 3      | 0x00000004                | Reset                                                     |

| NMI                 | 2                | 2 -      | 0x00000008                | Non-maskable interrupts                                   |

| HardFault           | 3                | - 1      | 0x0000000C                | Various hardware level failures                           |

| MemManage           | 4                | Settable | 0x00000010                | Memory management                                         |

| BusFault            | 5                | Settable | 0x00000014                | Prefetch refers to failure, memory access failure         |

| UsageFault          | 6                | Settable | 0x00000018                | Undefined instruction or illegal status                   |

| -                   | 7-10             | _        | 0x0000001C-<br>0x0000002B | reserve                                                   |

| SVcall              | 11               | Settable | 0x0000002C                | Implementation of system service call via SWI instruction |

| DebugMonitor        | 12               | Settable | 0x00000030                | Debug Monitor                                             |

| -                   | 13               | _        | 0x00000034                | Retain                                                    |

| PendSV              | 14               | Settable | 0x00000038                | Pendable system service request                           |

| Systick             | 15               | Settable | 0x0000003C                | System Beat Timer                                         |

The SysTick calibration value is set to 0x1196E and the SysTick clock frequency is set to HCLK. If the HCLK clock is set to 72MHz, the SysTick interrupt will respond once every 1ms.

Table 4-2 Interrupt vector table

| Interrupt<br>Sequence number | Vector<br>number | Peripheral interrupt description | Vector address |

|------------------------------|------------------|----------------------------------|----------------|

| IRQ0                         | 16               | lvd_int                          | 0x0000_0040    |

| IRQ1                         | 17               | uart0_int                        | 0x0000_0044    |

| IRQ2                         | 18               | uart1_int                        | 0x0000_0048    |

| IRQ3                         | 19               | spi0_int                         | 0x0000_004C    |

| IRQ4                         | 20               | spil_int                         | 0x0000_0050    |

| IRQ5                         | 21               | gpioa_int                        | 0x0000_0054    |

| IRQ6                         | 22               | gpiob_int                        | 0x0000_0058    |

| IRQ7                         | 23               | gpioe_int                        | 0x0000_005C    |

| IRQ8                         | 24               | wkpnd_int                        | 0x0000_0060    |

| IRQ9                         | 25               | timer0_int                       | 0x0000_0064    |

| IRQ10                        | 26               | timer1_int                       | 0x0000_0068    |

| IRQ11                        | 27               | timer2_int                       | 0x0000_006C    |

| IRQ12                        | 28               | timer3_int                       | 0x0000_0070    |

| IRQ13 | 29 | timer4_int      | 0x0000_0074 |

|-------|----|-----------------|-------------|

| IRQ14 | 30 | timer5_int      | 0x0000_0078 |

| IRQ15 | 31 | epwm_tzint      | 0x0000_007C |

| IRQ16 | 32 | epwm_etint      | 0x0000_0080 |

| IRQ17 | 33 | adkey_interrupt | 0x0000_0084 |

| IRQ18 | 34 | div_ovf_int     | 0x0000_0088 |

| IRQ19 | 35 | crc_dma_int     | 0x0000_008C |

| IRQ20 | 36 | comp_int        | 0x0000_0090 |

| IRQ21 | 37 | wdt_interrupt   | 0x0000_0094 |

| IRQ22 | 38 | eflash_int      | 0x0000_0098 |

| IRQ23 | 39 | adkey_int1      | 0x0000_009C |

| IRQ24 | 40 | _               | 0x0000_00A0 |

| IRQ25 | 41 | _               | 0x0000_00A4 |

| IRQ26 | 42 | _               | 0x0000_00A8 |

| IRQ27 | 43 | _               | 0x0000_00AC |

| IRQ28 | 44 | -               | 0x0000_00B0 |

| IRQ29 | 45 | _               | 0x0000_00B4 |

| IRQ30 | 46 | -               | 0x0000_00B8 |

| IRQ31 | 47 | -               | 0x0000_00BC |

# 4.4. External Interrupt/Event Controller (EXTI)

The External Interrupt and Time Controller (EXTI) manages external and internal asynchronous events/interrupts and generates corresponding event requests to the CPU/ interrupt controller and wake-up requests to power management. Each input line can be independently configured with the input type (pulse or suspend) and the corresponding trigger event (both rising or falling edges or both sides firing). Each input line can be masked independently. The suspend register holds the interrupt request for the status line.

# 4.4.1. Key features

The main features of the EXTI controller are as follows:

- Each interrupt/event has an independent trigger and mask

- Each interrupt has a dedicated status bit

- Supports interrupt/event requests for up to 20 pieces of software

- ullet Detect external signals with pulse widths below the APBO clock width

See the relevant parameters in the Electrical Characteristics section of the data book

## 4.4.2. Wake up Event Management

The TX32M2300 series can handle external or internal events to wake up the kernel (WFE). Wake events can be generated with the following configuration:

- An interrupt is enabled in the peripheral's control register, but not in the NVIC, while the SEVONPEND bit is enabled in the CPU's system control register. When the CPU recovers from the WFE, it needs to clear the interrupt suspend bit of the corresponding peripheral and the peripheral NVIC interrupt Channel suspend bit (in the NVIC Interrupt Clear Suspend register).

- Configure an external or internal EXTI line to be in event mode. When the CPU recovers from WFE, it does not have to clear the interrupt suspend bit or NVIC interrupt channel suspend bit of the corresponding peripheral because the suspend bit of the corresponding event line is not set.

## 5. Power Control

# 5.1. Power supply

The operating voltage (VCC) of the chip is 2.0V to 5.5V. This chip is designed with CAPLESS,

and there is no need to attach external capacitors to the built-in LDO output.

## 5.1.1. Voltage regulator

Regulator is always enabled after reset. In the case of low power consumption, you can enable the low power mode, PMUCONO.lpen as the power mode switching control bit.

## 5. 2. Power Manager

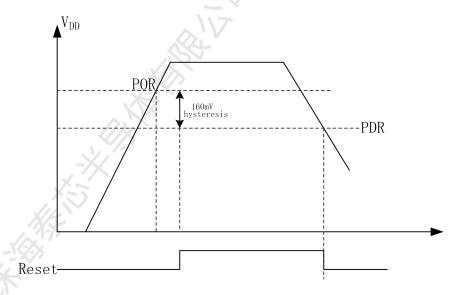

## 5.2.1. Power-on reset (POR) and power-off reset (PDR)

The TX32M2300 series has a complete power-on reset (POR) and power-off reset (PDR) circuit inside, when the supply voltage reaches 2.7V

When the system can work normally. When VDD is below the specified limit voltage VPOR/VPDR, the system remains in the reset state without the need for an external reset circuit.

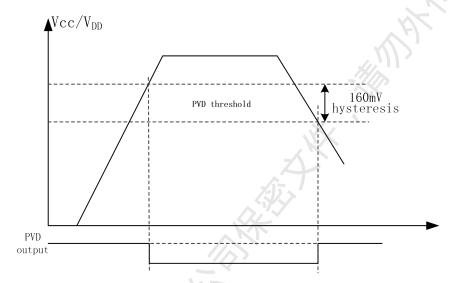

Figure 6-1 power-on reset and power-off reset

# 5. 2. 2. Programmable Voltage Monitor (PVD)

Two voltage detectors are integrated inside the TX32M2300 series, one detects the external

powered VCC and one detects the internal LDO output VDD. The LDO samples the capless structure and the VDD is not visible on the package. Both detection voltage thresholds are optional. When the system detects that the VCC or VDD voltage is lower than the configured voltage value, it can choose to trigger the system reset or enter the interrupt subfunction by enabling the PVD interrupt. This feature can be used to perform emergency shutdown tasks. The detection signal can be selected to pass through a burr filter circuit or directly detected, controlled by LVD\_CON.lvdvdc\_bps\_en and LVD\_CON.lvdvdd\_bps\_en.

Figure 6-2 Schematic diagram of PVD

### 5.3. Low Power Mode

After the system or power is reset, the microcontroller is running and the system clock is 256Khz internal RC. A variety of low-power modes can be used to save power when the CPU does not need to continue running, such as while waiting for an external event. The user needs to choose the best low-power mode based on the lowest power consumption, the fastest startup time, and the available wake source.

The TX32M2300 series is available in three low power modes:

- IDLE mode (CPU stops and all peripherals including the peripherals of the CPU, such as NVIC, system clock (SysTick), etc. are still running)

- STOP mode (CPU, most peripherals stop, can rely on other times to wake this mode after the chip continues to run)

- SLEEP mode (all clock sources stop, rely on external IO wake up, can choose

to reset the chip or continue running)

In addition, in run mode, power consumption can be reduced in one of the following ways:

- Reduce the system clock

- Turn off unused peripheral clocks on the APB and AHB buses

- Configure the frequency relationship between APB and AHB properly

# 5.4. Registers

# 5. 4. 1. Register base address

| Name | Base Address | Description        |

|------|--------------|--------------------|

| LVD  | 0x40000100   | LVD's base address |

# 5. 4. 2. Register list

| Offset Address | Name    | Ø₁.V | Description            |

|----------------|---------|------|------------------------|

| 0x00           | LVD_CON |      | Configuration register |

# 5. 4. 3. Register Details

#### 5. 4. 3. 1. LVD\_CON

| Bit(s) | Name                                     | Description                                   | R/W | Reset |

|--------|------------------------------------------|-----------------------------------------------|-----|-------|

|        | -1553                                    | The VDD voltage below the set threshold       |     |       |

| 31     | lvdvdd_pending                           | triggers pending                              | R   | 0     |

| *      |                                          | write O clean this bit                        |     |       |

|        |                                          | The VCC voltage below the set threshold       |     |       |

| 30     | lvdvcc_pending                           | triggers pending                              | R   | 0     |

|        |                                          | write 0 clean this bit                        |     |       |

| 29     | Reserved                                 |                                               | ı   | Ī     |

| 00.00  | 11 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 | Filter detects voltage signal low burr width  | DW  | 0     |