ISO9001:2015 quality management system controlled documents

# TX8C101x User manual

珠海泰芯半导体有限公司 Zhuhai Taixin Semiconductor Co., Limited

| 保密等级 | A          |

|------|------------|

| 发行日期 | 2023-08-31 |

# TX8C101x 用户手册

| 文件编号 | TX-WI-TX8C1010-RD02 |

|------|---------------------|

| 文件版本 | V2.8                |

### Revision records

| Date          | Version    | Description                                                                                                                                                                                                                                                     | Redactor      |

|---------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| 2023-08-31    | V2. 8      | 1, update the English name description of the company in the footer;                                                                                                                                                                                            | FWF           |

| 2023-08-30    | V2. 7      | 1, update the logo pattern;                                                                                                                                                                                                                                     | FWF           |

| 2023-08-21    | V2. 6      | 1, modify the description of the ADC reference voltage;                                                                                                                                                                                                         | FWF           |

| 2023-05-31    | V2. 5      | 1, modify the description of the ADC reference voltage;                                                                                                                                                                                                         | FWF           |

| 2023-05-17    | V2. 4      | <ol> <li>modify the description of GPIO low power wake-up, change to level wake-up;</li> <li>Move the detailed description of the wake-up register to low power management;</li> <li>Modify the description of the ADC's internal reference voltage;</li> </ol> | FWF           |

| 2023-02-03    | V2. 3      | 1. Solve the problem of garbled code when some devices are opened to read;                                                                                                                                                                                      | HLW           |

| 2022-10-20    | V2. 2      | 1, modify the comparator part of the functional description; 2, modify the LP_CON description;                                                                                                                                                                  | ZJ, HLW       |

| The 2022-8-10 | V2. 1      | Modify the frequency division ratio description of the ADC module.                                                                                                                                                                                              | HLW           |

| The 2022-7-28 | V2. 0      | Change the model to TX8C101x, unifying the TX8C1010 and TX8C1011 series.                                                                                                                                                                                        | HLW           |

| The 2022-7-21 | V1. 13     | Amend Section 1 to reduce package model number.                                                                                                                                                                                                                 | ZJ            |

| The 2022-4-17 | V1. 12     | Fix SPI_CON register bit2 misdescription of sampling pattern.                                                                                                                                                                                                   | YLC           |

| The 2022-3-18 | V1. 11     | Fix the error description for bits 1 and 0 of the AIP_CON1 register.                                                                                                                                                                                            | ZJ            |

| The 2022-3-10 | V1. 10     | Modify the description of the n-tube p-tube switch function of the analog comparator CON4.                                                                                                                                                                      | YLC           |

| The           | V1.9       | Modified description of analog comparator PO3 PAD                                                                                                                                                                                                               | ZJ            |

| 泰心半导          | 14<br>ctor | Short circu來海康思率時本有限坚計ion.  Zhuhai Taixin Semiconductor 珠海市高新区 Co., Limited                                                                                                                                                                                     | <br> 港湾一号科创园港 |

珠海市高新区港湾一号科创园港 11 栋 3 楼

版权所有 侵权必究

| 保密等组   | 级     |             |     | 文件编号 | TX-WI-TX8C1010-                                                                         | -RD02      |         |   |

|--------|-------|-------------|-----|------|-----------------------------------------------------------------------------------------|------------|---------|---|

| 发行日基   | 期     | 2023-08-    | -31 |      | TX8C101x 用户手册                                                                           | 文件版本       | V2.8    |   |

|        | 2022- | -2-25       | ·   |      |                                                                                         | ·          |         | , |

|        |       | he<br>-2-23 | V1. | 8    | Fixed TX8C101xS014 PIN8 pin P14 error d                                                 | escription | ZJ      |   |

|        |       | he<br>-2-11 | V1. | 7    | Flash control module Add address instructions                                           |            | HLW     |   |

|        | 2021- | -12-28      | V1. | 6    | Change encapsulation information for SOP8                                               |            | ZJ, HLW |   |

| -<br>- | 2021- | -12-17      | V1. | 5    | Fix SYS_CON2 bit 6 and 7 description err                                                | or, modify | ZJ      |   |

|        | 2021- | -12-07      | V1. | 4    | Add the pin diagram for the TX8C101xQF16.                                               |            | HLW     |   |

|        | 2021- | -08-23      | V1. | 0    | Initial version, subject to future update notice, please contact our staff for version. |            | ZJ, HLW |   |

# 保密等级 A 发行日期 The 2022-8-10

# TX8C101x 用户手册

| 文件编号 | TX-WI-TX8C1010-RD02 |

|------|---------------------|

| 文件版本 | V1. 13              |

### Contents

| TX8C101x owner's manual                      |     |

|----------------------------------------------|-----|

| 1 Overview of the product                    |     |

| 1.1. Instructions                            | . 1 |

| 1.2. Features                                | . 2 |

| 2. Central Processing Unit                   |     |

| 2.1. Accumulator (ACC)                       |     |

| 2.2. Register (B)                            | . 6 |

| 2.3. Stack Pointer Register (SP)             | . 7 |

| 2.4. Stack Pointer Register (SPH)            | . 7 |

| 2.5. Data Pointer Register (DPTRO/DPTR1)     | 8   |

| 2.6. Data Pointer Control Register (DPCFG)   | 9   |

| 2.7. Program Status Register (PSW)           | 10  |

| 2.8. Program Counter (PC)                    | 10  |

| 3. Memory                                    | 11  |

| 3.1. Program memory                          | 11  |

| 3. 2. XDATA                                  |     |

| 3. 3. IDATA                                  | 13  |

| 3.4. SFR space                               | 15  |

| 4. System clock                              | 16  |

| 4.1. Overview of the clock system            | 16  |

| 4.2. Main functions of clock system          | 16  |

| 4.3. Clock system block diagram              | 17  |

| 4.4. System oscillator                       | 18  |

| 4.4.1. Internal low speed RC oscillator      | 18  |

| 4.4.2. Internal high speed RC oscillator     | 18  |

| 4.4.3. External low speed crystal oscillator |     |

| 5. Reset system                              |     |

| 5.1. Power on reset                          | 19  |

| 5.2. Power down reset power down             | 19  |

珠海泰芯半导体有限公司 Zhuhai Taixin Semiconductor Co., Limited

保密等级 文件编号 TX-WI-TX8C1010-RD02 TX8C101x 用户手册 The 2022-8-10 V1.13 发行日期 文件版本

珠海泰芯半导体有限公司 Zhuhai Taixin Semiconductor Co., Limited

| 保密等级 | A              | myo od od HI A Z III                | 文件编号 | TX-WI-TX8C1010-RD02 |

|------|----------------|-------------------------------------|------|---------------------|

| 发行日期 | The 2022-8-10  | TX8C101x 用户手册                       | 文件版本 | V1. 13              |

|      | 7. 3. 20       | . IO_MAP1                           |      | 50                  |

|      |                | . SYS_PND                           |      |                     |

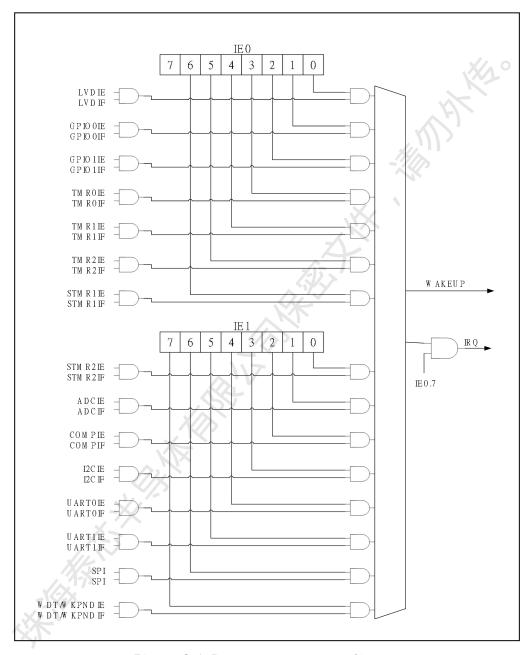

|      | 8. Interrupt t | he system                           |      | 51                  |

|      | 8.1. Inter     | rupt overview                       |      | 51                  |

|      | 8.2. Struc     | tural block diagram                 |      | 52                  |

|      | 8.3. Inter     | rupt vector table                   |      | 53                  |

|      |                | ter list                            |      | A                   |

|      | 8.5. Regis     | ter details                         |      | 54                  |

|      |                | IEO                                 |      |                     |

|      | 8. 5. 2.       | Internet Explorer 1                 |      | 55                  |

|      |                | IP0                                 |      |                     |

|      | 8. 5. 4.       | IP1                                 | -/// | 57                  |

|      | 8.6. Inter     | rupt priority and interrupt nesting |      | 58                  |

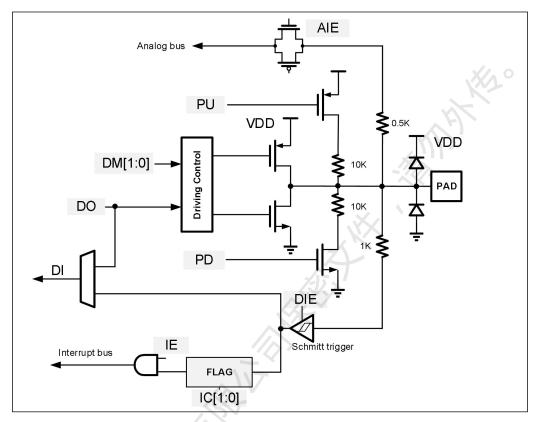

|      | 9. I/O ports   |                                     |      | 59                  |

|      | 9.1. Struc     | ture block diagram                  |      | 59                  |

|      | 9.2. Regis     | ter list                            |      | 59                  |

|      | 9.3. Regis     | ter detail                          |      | 61                  |

|      | 9. 3. 1.       | P0                                  |      | 61                  |

|      |                | PO_PU                               |      |                     |

|      | 9. 3. 3.       | PO_PD                               |      | 62                  |

|      |                | PO_MDO                              |      |                     |

|      | 9. 3. 5.       | PO_MD1                              |      | 64                  |

|      |                | P0_AF0                              |      |                     |

|      | 9. 3. 7.       | P0_AF1                              |      | 66                  |

|      | 9. 3. 8.       | P0_TRG0                             |      | 67                  |

|      | 9. 3. 9.       | P0_TRG1                             |      | 67                  |

|      | 9. 3. 10       | . PO_PND                            |      | 68                  |

|      | 9. 3. 11       | .PO_IMK                             |      | 69                  |

|      | 9. 3. 12       | .PO_AIOEN                           |      | 70                  |

|      | 9. 3. 13       | . PO_DRV                            |      | 71                  |

|      | 9. 3. 14       | . PO_OD                             |      | 72                  |

|      | 9. 3. 15       | . P1                                |      | 73                  |

|      | 9. 3. 16       | . P1_PU                             |      | 73                  |

|      |                | . P1_PD                             |      |                     |

|      | 9. 3. 18       | . P1_MD0                            |      | 74                  |

|      |                | _<br>.P1_MD1                        |      |                     |

|      |                | . P1_AF0                            |      |                     |

|      |                | . P1_AF1                            |      |                     |

| 保密等级 | A               | WY00101 H H T III      | 文件编号   | TX-WI-TX8C1010-F |

|------|-----------------|------------------------|--------|------------------|

| 发行日期 | The 2022-8-10   | TX8C101x 用户手册          | 文件版本   | V1. 13           |

|      | 9. 3. 22        | P1_TRGO                |        | 77               |

|      | 9. 3. 23.       | P1_TRG1                |        | 78               |

|      | 9. 3. 24        | P1_PND                 |        | 79               |

|      |                 | P1_IMK                 |        |                  |

|      |                 | P1_AIOEN               |        |                  |

|      |                 | P1_DRV                 |        |                  |

|      |                 | P1_0D                  |        |                  |

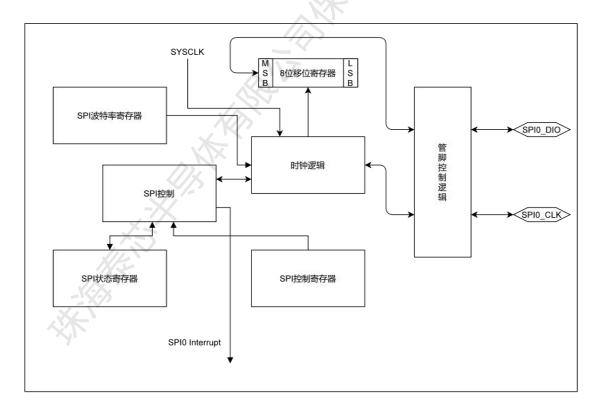

|      | 10. SPI module. |                        |        | 83               |

|      | 10.1. Func      | tional Overview        |        | 83               |

|      | 10.2. Bloc      | k diagram of modules   |        | 83               |

|      | 10.3. Regi      | ster list              |        | 84               |

|      | 10.4. Regi      | ster details           | 11/2)  | 84               |

|      |                 | SPIO_CON               | -////  |                  |

|      |                 | SPIO BAUD              |        |                  |

|      |                 | SPIO_DATA              |        |                  |

|      |                 | SPIO_STA               |        |                  |

|      |                 | process instructions   |        |                  |

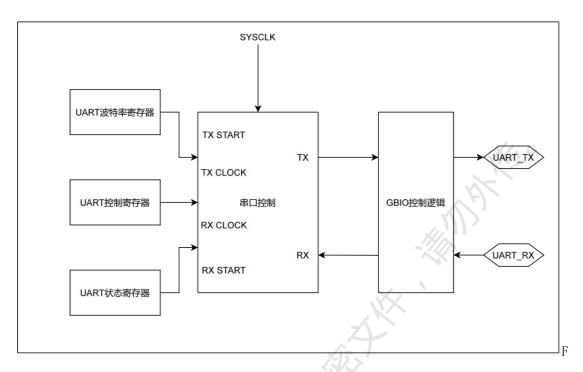

|      | 11 UARTO/1 mod  | dule                   | •••••• | 86               |

|      |                 | view of functions      |        |                  |

|      |                 | k diagram of modules   |        |                  |

|      |                 | 117                    |        |                  |

|      | 11.3. Regi      | ster list              |        | 87               |

|      | 11.4. Regi      | ster details           |        | 88               |

|      | 11. 4. 1.       | UARTO_CON              |        | 88               |

|      | 11. 4. 2.       | UARTO_STA              |        | 89               |

|      | 11. 4. 3.       | UARTO_BAUDO            |        | 89               |

|      | 11. 4. 4        | UARTO_BAUD1            |        | 90               |

|      | 11. 4. 5        | UARTO_DATA             |        | 90               |

|      | 11. 4. 6        | UART1_CON              |        | 90               |

|      | 11. 4. 7        | UART1_STA              |        | 91               |

|      | 11. 4. 8        | UART1_BAUD0            |        | 92               |

|      |                 | UART1_BAUD1            |        |                  |

|      | 11. 4. 1        | O. UART1_DATA          |        | 92               |

|      | 11.5. Usag      | e process instructions |        | 93               |

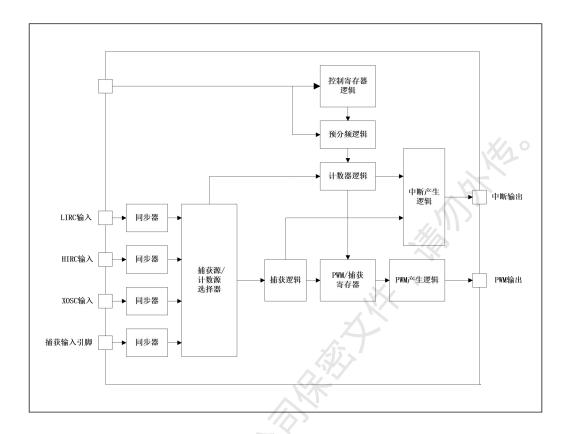

|      | 12. Basic Time: | r O/1 module           |        | 93               |

|      | 12.1. Func      | tional Overview        |        | 93               |

|      | 12.2. Bloc      | κ diagram of modules   |        | 94               |

| 保密等级 | A              | WY00101 H 4 T HI                  | 文件编号  | TX-WI-TX8C1010-RD02 |

|------|----------------|-----------------------------------|-------|---------------------|

| 发行日期 | The 2022-8-10  | TX8C101x 用户手册                     | 文件版本  | V1. 13              |

|      | 12.3. Regi     | ster list                         |       | 94                  |

|      | 12.4. Regi     | ster details                      |       | 95                  |

|      | 12. 4. 1       | . TMRO_CONL                       |       | 95                  |

|      | 12. 4. 2       | . TMRO_CONH                       |       | 96                  |

|      | 12.4.3         | . TMRO_CNTL                       |       | 97                  |

|      | 12. 4. 4       | . TMRO_PRL                        |       | 97                  |

|      | 12. 4. 5       | . TMRO_PWML                       |       | 97                  |

|      |                | TMR1_CONL                         |       |                     |

|      |                | TMR1_CONH                         |       |                     |

|      |                | TMR1_CNTL                         |       |                     |

|      |                | TMR1_PRL                          |       |                     |

|      |                | O. TMR1_PWML                      | 1/1/2 |                     |

|      | 12.5. Use      | process instructions              |       | 100                 |

|      |                | . Counter/Timer mode of operation |       |                     |

|      |                | . Capture operating mode          |       |                     |

|      |                | . PWM working mode                |       |                     |

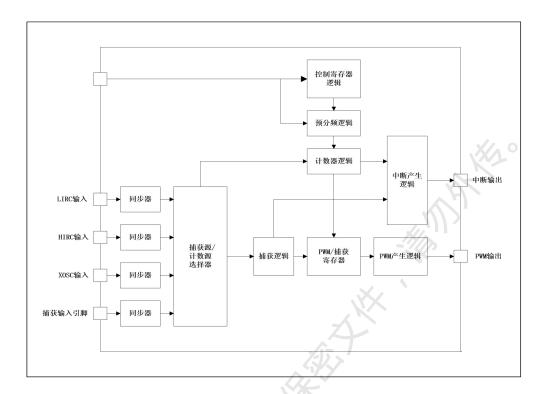

|      |                | r2 module                         |       |                     |

|      | 13.1. Over     | view of features                  |       | 102                 |

|      | 13.2. Bloc     | k diagram of modules              |       | 103                 |

|      | 13.3. Regi     | ster list                         |       | 103                 |

|      | 13.4. Regi     | ster details                      |       | 104                 |

|      | 13. 4. 1       | . TMR2_CONL                       |       | 104                 |

|      |                | . TMR2_CONH                       |       |                     |

|      |                | . TMR2_CNTL                       |       |                     |

|      | 13. 4. 4       | .TMR2_CNTH                        |       | 106                 |

|      | 13. 4. 5       | . TMR2_PRL                        |       | 106                 |

|      | 13. 4. 6       | TMR2_PRH                          |       | 106                 |

|      |                | . TMR2_PWML                       |       |                     |

|      | 13. 4. 8       | . TMR2_PWMH                       |       | 107                 |

|      | 13.5. Use      | process instructions              |       | 107                 |

|      | 13. 5. 1       | . Counter/Timer operation mode    |       | 107                 |

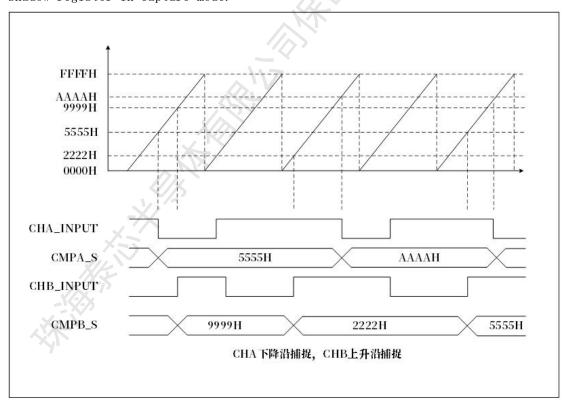

|      | 13. 5. 2       | . Capture operating mode          |       | 108                 |

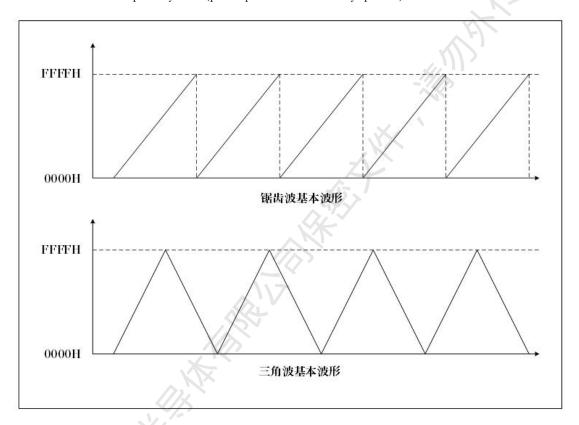

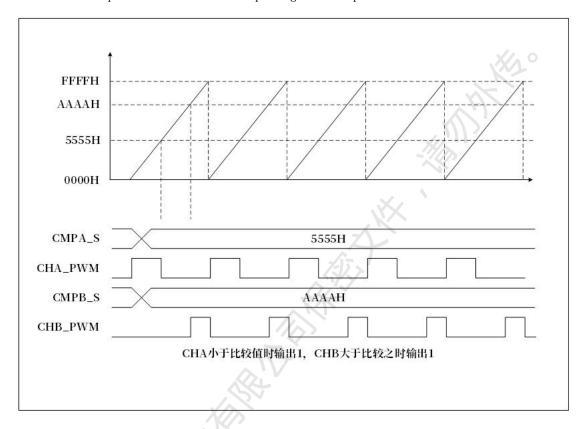

|      | 4              | . PWM working mode                |       |                     |

|      | 14. Advanced T | imer 1/2 module                   |       | 109                 |

|      | 14.1. Over     | view of features                  |       | 109                 |

|      | 14. 1. 1       | . Basic Actions                   |       | 110                 |

|      | 14. 1. 2       | . Clock Source Selection          |       | 114                 |

|      | 14.1.3         | . Counting directions             |       | 114                 |

| 保密等级 | A             | #¥00101 ⊞ H:              | <b>==</b> nn                            | 文件编号     | TX-WI-TX8C1010-RI |

|------|---------------|---------------------------|-----------------------------------------|----------|-------------------|

| 发行日期 | The 2022-8-10 | TX8C101x 用户 <sup>3</sup>  | 于加                                      | 文件版本     | V1. 13            |

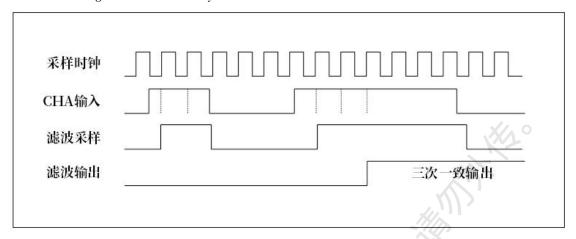

|      | 14. 1. 4.     | Digital filtering         |                                         |          | 115               |

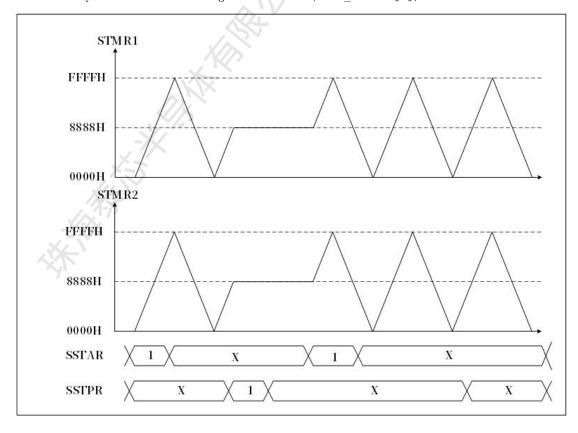

|      | 14. 1. 5.     | Software synchronization  |                                         |          | 116               |

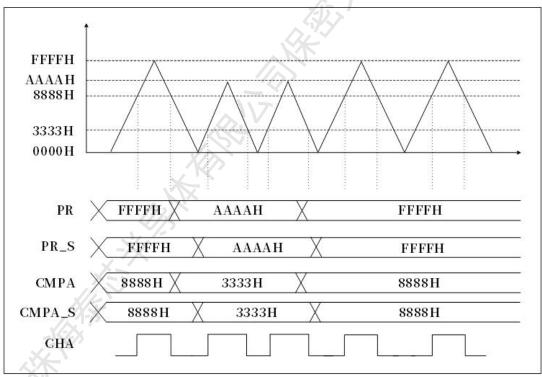

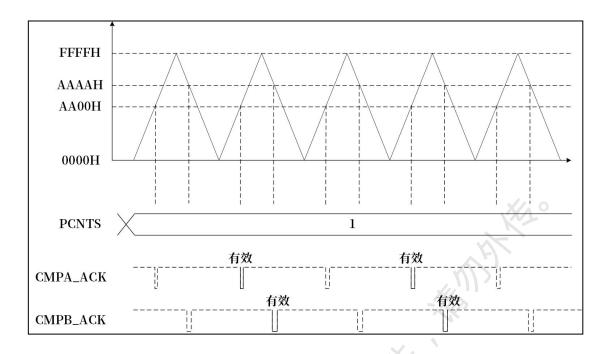

|      | 14. 1. 6.     | . Cache functionality     |                                         |          | 117               |

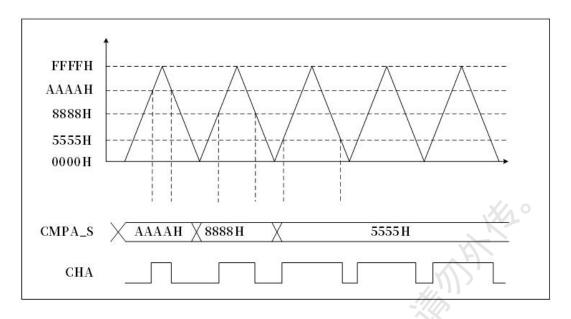

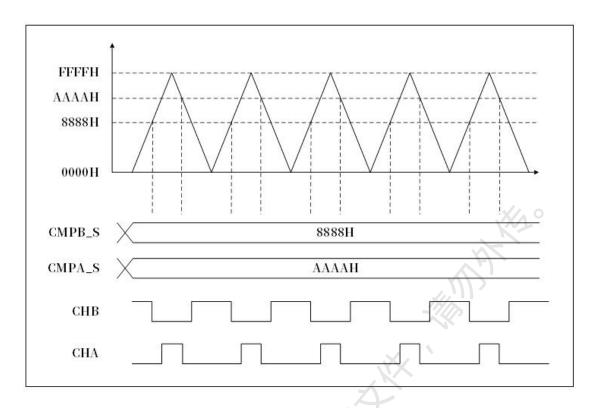

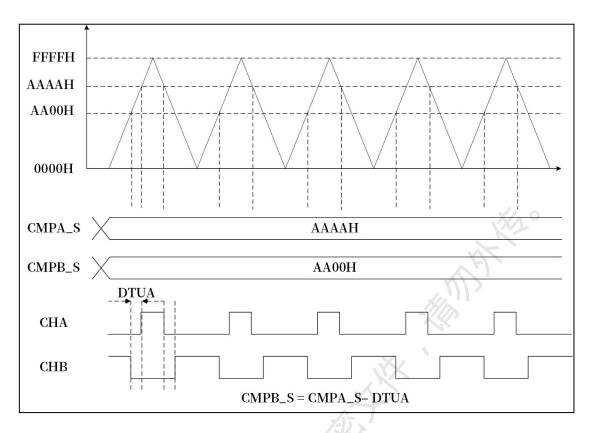

|      | 14. 1. 7.     | General PWM output        |                                         |          | 119               |

|      | 14. 1. 8.     | . Cycle interval response |                                         |          | 122               |

|      | 14. 1. 9.     | Protection mechanisms     |                                         |          | 123               |

|      | 14. 1. 10     | O. Interrupt instructions |                                         |          | 124               |

|      | 14. 1. 1      | 1. Brake protection       |                                         |          | 124               |

|      | 14. 1. 13     | 2. Internal interconnect  |                                         |          | 124               |

|      | 14. 1. 13     | 3. Infrared function      |                                         |          | 125               |

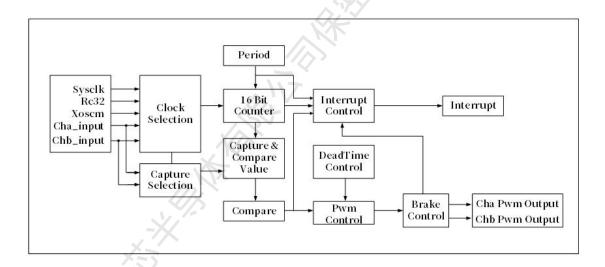

|      | 14.2. Block   | k diagram of the module   |                                         |          | 125               |

|      | 14.3. Regis   | ster list                 |                                         |          | 125               |

|      | 14.4. Regis   | ster details              |                                         | <u> </u> | 127               |

|      | 14. 4. 1.     | STMR1_CR                  |                                         |          | 127               |

|      | 14. 4. 2.     | STMR1_FCONR               |                                         | <b>\</b> | 128               |

|      | 14. 4. 3.     | STMR1_CNTL                |                                         |          | 129               |

|      | 14. 4. 4.     | STMR1_CNTH                | 70                                      |          | 129               |

|      | 14. 4. 5.     | STMR1_PRL                 |                                         |          | 129               |

|      | 14. 4. 6.     | STMR1_PRH                 | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |          | 129               |

|      | 14. 4. 7.     | STMR1_CMPAL               |                                         |          | 130               |

|      | 14. 4. 8.     | STMR1_CMPAH               |                                         |          | 130               |

|      | 14. 4. 9.     | STMR1_CMPBL               |                                         |          | 130               |

|      |               | O. STMR1_CMPBH            |                                         |          |                   |

|      | 14. 4. 1      | 1. STMR1_VPERR            |                                         |          | 131               |

|      | 14. 4. 13     | 2. STMR1_DTUA             |                                         |          | 132               |

|      | 14. 4. 13     | 3. STMR1_BRAKE            |                                         |          | 132               |

|      | 14. 4. 1      | 4. STMR1_DTR              |                                         |          | 134               |

|      | 14. 4. 1      | 5. STMR1_PCONRA           |                                         |          | 135               |

|      | 14. 4. 10     | 6. STMR1_PCONRB           |                                         |          | 136               |

|      | 14. 4. 1      | 7. STMR1_IE               |                                         |          | 137               |

|      | 14. 4. 1      | 8. STMR1_SR               |                                         |          | 138               |

|      | 14. 4. 1      | 9. STMR2_CR               |                                         |          | 140               |

|      | 14. 4. 20     | O. STMR2_FCONR            |                                         |          | 140               |

|      | 14. 4. 2      | 1. STMR2_PRL              |                                         |          | 141               |

|      | 14. 4. 2      | 2. STMR2_PRH              |                                         |          | 141               |

|      | 14. 4. 23     | 3. STMR2_CMPAL            |                                         |          | 141               |

|      | 14. 4. 2      | 4. STMR2_CMPAH            |                                         |          | 142               |

|      | 14. 4. 2      | 5. STMR2_CMPBL            |                                         |          | 142               |

|      | 14. 4. 20     | 6. STMR2_CMPBH            |                                         |          | 142               |

|      | 14. 4. 2      | 7. STMR2_VPERR            |                                         |          | 143               |

|      | 14. 4. 2      | 8. STMR2_DTUA             |                                         |          | 144               |

| 保密等级 | A                   | TV0C101 甲內毛III                | 文件编号 | TX-WI-TX8C1010-RD02 |  |  |  |

|------|---------------------|-------------------------------|------|---------------------|--|--|--|

| 发行日期 | The 2022-8-10       | TX8C101x 用户手册                 | 文件版本 | V1. 13              |  |  |  |

|      |                     | 9. STMR2_BRAKE                |      |                     |  |  |  |

|      |                     | O. STMR2_DTR                  |      |                     |  |  |  |

|      |                     | 1. STMR2_PCONRA               |      |                     |  |  |  |

|      |                     | 2. STMR2_PCONRB               |      |                     |  |  |  |

|      | 14. 4. 33. STMR2_IE |                               |      |                     |  |  |  |

|      |                     | 5. STMR_ALLCON                |      |                     |  |  |  |

|      | 14.5. Use           | process instructions          |      | 152                 |  |  |  |

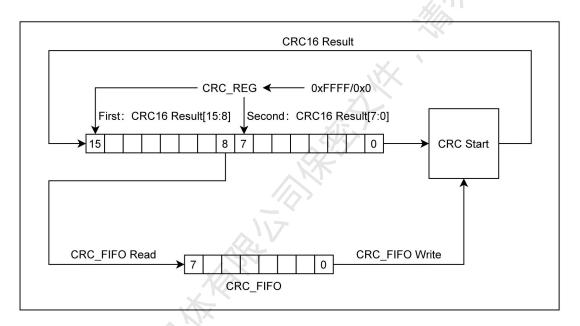

|      | 15. CRC16 modu      | le                            |      | 153                 |  |  |  |

|      |                     | ure Overview                  | 4//  |                     |  |  |  |

|      |                     | c functionality               |      |                     |  |  |  |

|      | 15.3. Bloc          | k diagram of modules          | -100 | 154                 |  |  |  |

|      | 15.4. Regi          | ster list                     |      | 154                 |  |  |  |

|      | 15.5. Regi          | ster details                  |      | 155                 |  |  |  |

|      | 15. 5. 1            | . CRC_REG                     |      | 155                 |  |  |  |

|      | 15. 5. 2            | CRC_FIFO                      |      | 155                 |  |  |  |

|      |                     | process instructions          |      |                     |  |  |  |

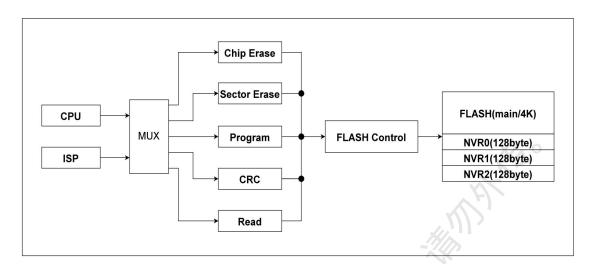

|      | 16. FLASH Cont      | roller module                 |      | 156                 |  |  |  |

|      | 16.1. Fund          | tional Overview               |      | 156                 |  |  |  |

|      |                     | k diagram of the module       |      |                     |  |  |  |

|      | 16.3. Regi          | ster list                     |      | 157                 |  |  |  |

|      | 16.4. Regi          | ster details                  |      | 158                 |  |  |  |

|      | 16. 4. 1            | . FLASH_CON                   |      | 158                 |  |  |  |

|      | 16. 4. 2            | . FLASH_STA                   |      | 158                 |  |  |  |

|      | 16. 4. 3            | FLASH_DATA                    |      | 159                 |  |  |  |

|      |                     | FLASH_TIMO                    |      |                     |  |  |  |

|      |                     | FLASH_TIM1                    |      |                     |  |  |  |

|      |                     | FLASH_CRCLEN                  |      |                     |  |  |  |

|      |                     | FLASH_PSWD                    |      |                     |  |  |  |

|      | ~ / /               | FLASH_ADDR                    |      |                     |  |  |  |

|      | 71                  | . FLASH_TRIM                  |      |                     |  |  |  |

|      |                     | process instructions          |      |                     |  |  |  |

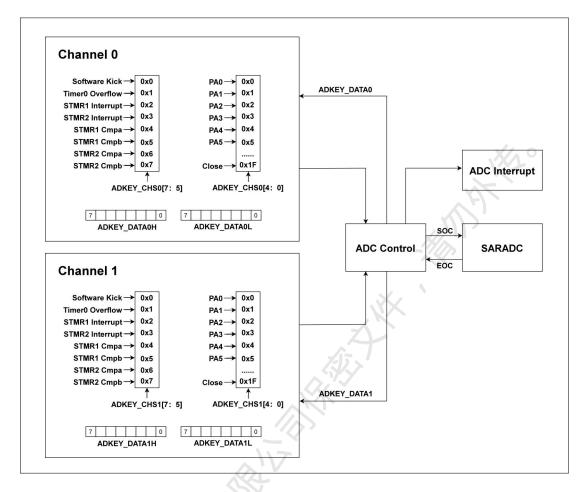

|      |                     | digital Converter (ADC)       |      |                     |  |  |  |

|      | 17.1. Fund          | tional Overview               |      | 164                 |  |  |  |

|      | 17.2. Basi          | c functions                   |      | 165                 |  |  |  |

|      | 17. 2. 1            | . Single-channel Trigger mode |      | 165                 |  |  |  |

| 保密等级 | A             | WY00101 HI 2 T III                           | 文件编号  | TX-WI-TX8C1010-RD02 |

|------|---------------|----------------------------------------------|-------|---------------------|

| 发行日期 | The 2022-8-10 | TX8C101x 用户手册                                | 文件版本  | V1. 13              |

|      | 17. 2. 2      | . Dual Channel Trigger mode                  |       | 165                 |

|      | 17. 2. 3      | . Single channel Trigger Delay mode          |       | 166                 |

|      | 17. 2. 4      | . Analog calibration/digital calibration     |       | 166                 |

|      | 17.3. Bloc    | k diagram of the module                      |       | 167                 |

|      | 17.4. Regi    | ster list                                    |       | 167                 |

|      | 17.5. Regi    | ster details                                 |       | 168                 |

|      | 17. 5. 1      | . ADC_CFG0                                   | ••••• | 168                 |

|      | 17. 5. 2      | . ADC_CFG1                                   |       | 169                 |

|      | 17. 5. 3      | . ADC_CFG2                                   |       | 170                 |

|      | 17. 5. 4      | . ADC_CFG3                                   |       | 170                 |

|      |               | . ADC_STA                                    |       |                     |

|      |               | . ADC_DATAHO                                 |       |                     |

|      |               | . ADC_DATALO                                 |       |                     |

|      |               | . ADC_DATAH1                                 |       |                     |

|      | 17. 5. 9      | . ADC_DATAL1                                 |       | 173                 |

|      | 17. 5. 1      | O. ADC_CHSO                                  |       | 173                 |

|      | 17. 5. 1      | 1. ADC_CHS1                                  | ••••• | 174                 |

|      |               | process instructions                         |       |                     |

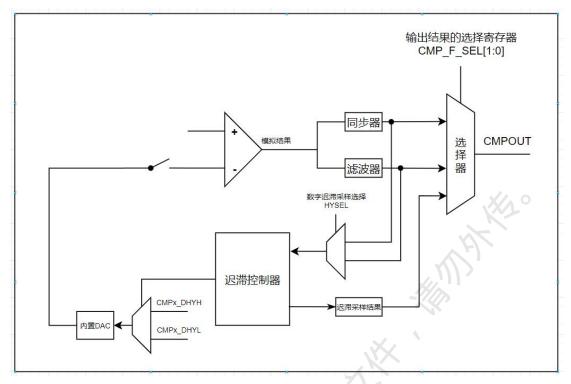

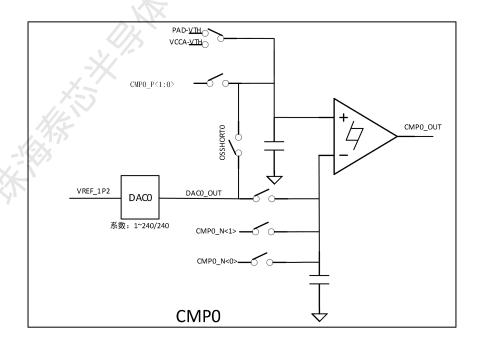

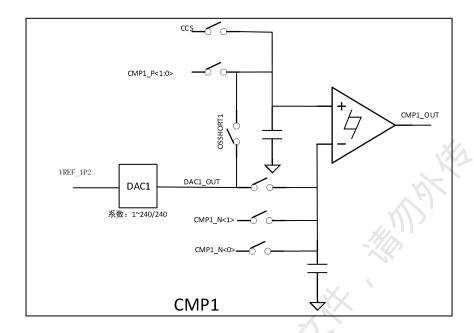

|      |               | parator (CMPO/1)                             |       |                     |

|      | 18.1. Feat    | ure overview                                 |       | 176                 |

|      | 18.2. Func    | tion instructions                            |       | 177                 |

|      | 18. 2. 1      | . Description of digital filter function     |       | 177                 |

|      | 18. 2. 2      | . Description of digital hysteresis function | on    | 177                 |

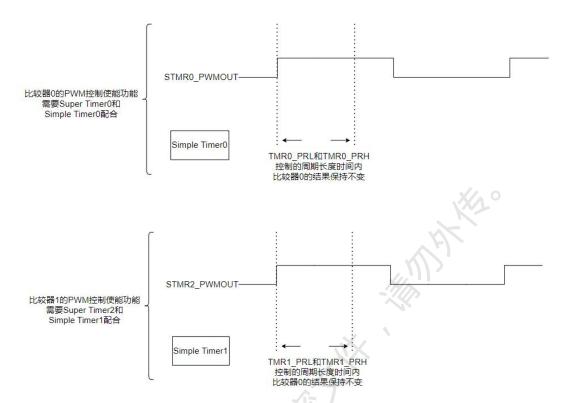

|      | 18. 2. 3      | . About PWM control comparator enable        |       | 178                 |

|      | 18.3. Bloc    | k diagram of the module                      |       | 179                 |

|      | 18.4. Pin     | correspondence table                         |       | 180                 |

|      | 18.5. List    | of registers                                 |       | 181                 |

|      | 18.6. Regi    | ster details                                 |       | 182                 |

|      | 18. 6. 1      | . CMPO_CONO                                  |       | 182                 |

|      | 18. 6. 2      | . CMPO_CON1                                  |       | 182                 |

|      | 18. 6. 3      | . CMPO_CON2                                  |       | 183                 |

|      | 18. 6. 4      | . CMPO_CON3                                  |       | 184                 |

|      | 18. 6. 5      | . CMPO_CON4                                  |       | 185                 |

|      | 18. 6. 6      | CMPO_DACO                                    |       | 186                 |

|      | 18. 6. 7      | . CMPO_DAC1                                  |       | 187                 |

|      | 18. 6. 8      | . CMP1_CONO                                  |       | 187                 |

|      | 18. 6. 9      | . CMP1_CON1                                  |       | 188                 |

|      | 18. 6. 1      | O. CMP1_CON2                                 |       | 188                 |

| 保密等级 | A              | 7.00101 田内式 III      | 文件编号     | TX-WI-TX8C1010-RD |

|------|----------------|----------------------|----------|-------------------|

| 发行日期 | The 2022-8-10  | TX8C101x 用户手册        | 文件版本     | V1. 13            |

|      | 18. 6. 1       | 1. CMP1_CON3         |          | 189               |

|      | 18. 6. 1       | 2. CMP1_CON4         |          | 190               |

|      | 18. 6. 1       | 3. CMP1_DACO         |          | 191               |

|      | 18. 6. 1       | 4. CMP1_DAC1         |          | 191               |

|      | 18. 6. 1       | 5. CMP_CON           |          | 192               |

|      | 18. 6. 1       | 6. CMP_STA           |          | 192               |

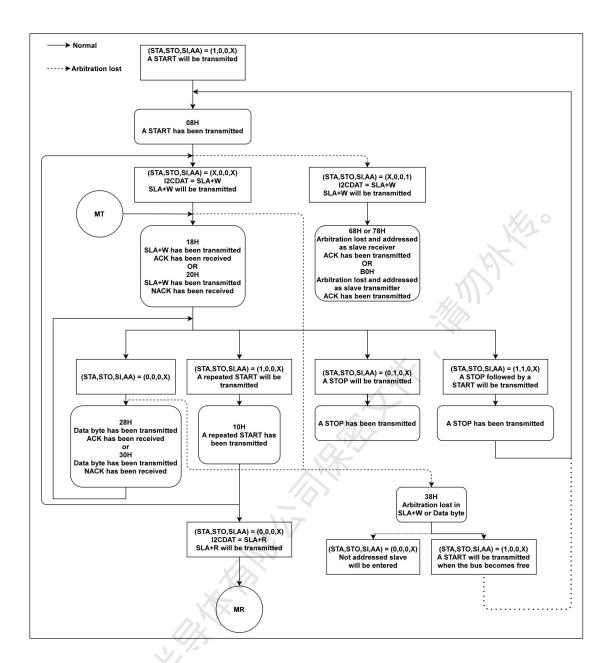

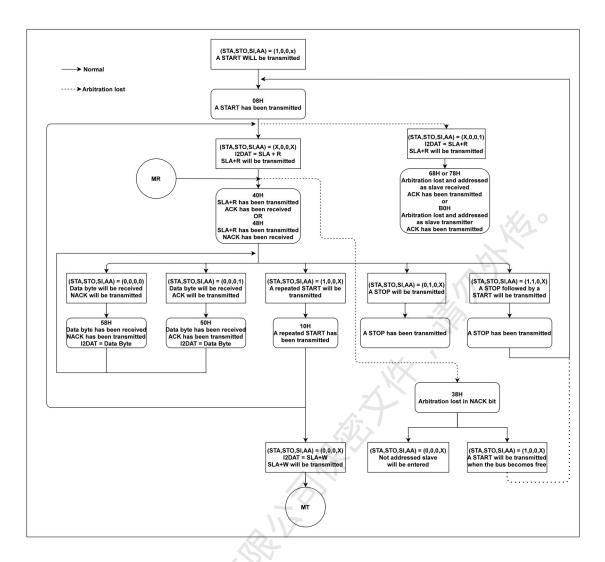

|      | 19. I2C module |                      |          | 193               |

|      | 19.1. Over     | view of features     |          | 193               |

|      | 19.2. Func     | tional Description   |          | 194               |

|      | 19. 2. 1       | Host sent            |          | 194               |

|      | 19. 2. 2       | Host receives        |          | 195               |

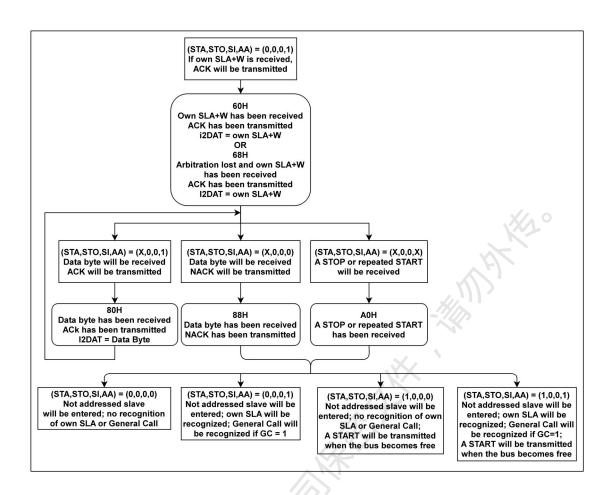

|      | 19. 2. 3       | Slave reception      |          | 196               |

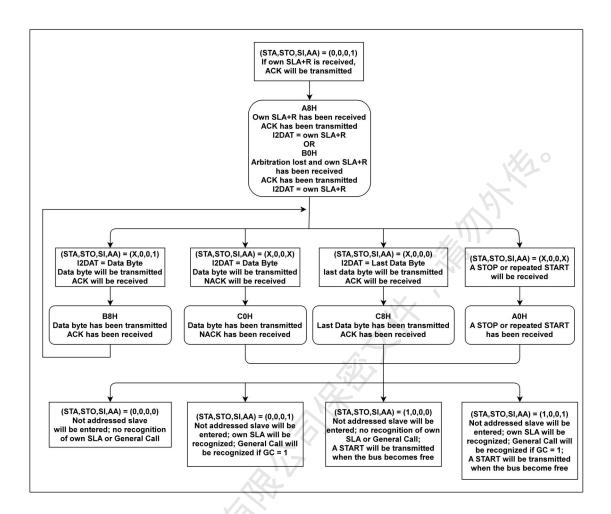

|      | 19. 2. 4       | Send from slave      | ./////   | 198               |

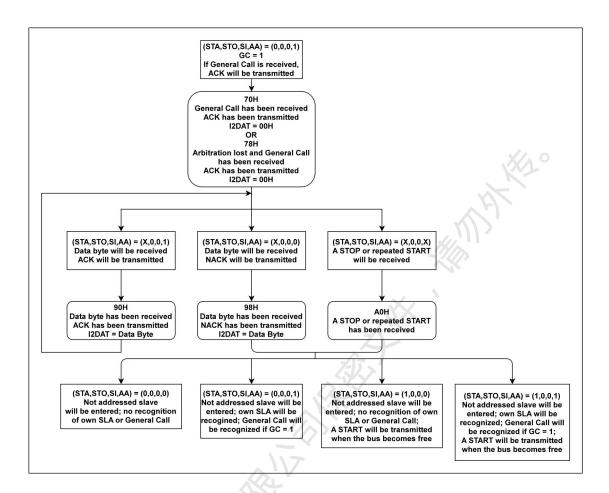

|      | 19. 2. 5       | Broadcast mode       |          | 199               |

|      | 19.3. Regi     | ster list            | <u> </u> | 199               |

|      | 19.4. Regi     | ster details         |          | 200               |

|      | 19. 4. 1       | 12C0_CON             |          | 200               |

|      | 19. 4. 2       | 12C0_STA             |          | 201               |

|      |                | 12C0_ADR             |          |                   |

|      | 19. 4. 4       | I2CO_DATA            |          | 202               |

|      | 19.5. Use      | process instructions |          | 202               |

# 1. Product Overview

### 1.1. Instructions

TX8C101x is a high performance and low power 8051 core MCU, operating at a maximum frequency of 32MHz, with built-in 4K+256 bytes flash memory (supporting EEPROM-like) and 512 bytes SRAM.

Analog resources: 1 12-bit 200Ksps ADC, 2 multi-function comparators.

Timers, PWM resources (both are mutually exclusive functions and cannot be used simultaneously with the same Timer) :

- 2 16-bit advanced timers, capable of supporting 2 pairs of complementary outputs or 4 independent PWM outputs (same cycle, independently configured duty cycle)

- 1 16-bit general purpose timer (both support Capture, Count, PWM functions)

- 28-bit general purpose timers (can be combined into 116-bit general purpose timer, both support Capture, Count, PWM functions)

Standard communication interface: 1 SPI interface, 2 UART interface, 1 IIC interface (only TX8C1011 series support).

It supports a wide range of voltage supply, the working voltage is  $2.4V^{\sim}$  5.5V (can support battery application scenarios), and the working temperature range is  $-40^{\circ}$ C  $^{\sim}$  85°C. A variety of power-saving operation modes ensure the requirements of low-power applications, and the lowest power consumption mode is 3uA.

TX8C1010 provides SOP8, MSOP10, SOP14, SOP16, QFN16 a total of 5 kinds of packaging forms, according to different packaging forms, the configuration of peripheral resources in the device is not the same.

Application occasions:

- Small appliances

- E-cigarettes

- Bluetooth charging bin, wireless charging

- Toys

### 1.2. Features

### • Kernel

- Ultra Fast 8051 core (1T)

- ➤ Instructions are fully compatible with traditional 8051

- > Maximum working frequency: 32MHz

- > 14 interrupt sources, support hardware two-level priority

- > Support for online downloads

- Support for code encryption

- Supports live burning

- > TX8C1011 series supports online debugging function

### Operating voltage

> 2.4V~5.5V wide voltage range power supply

### Memory

- > 4K+256 bytes Flash for storing user code and EEPROM-like support (typical value of 100,000 erases and writes)

- > 512 bytes of RAM

### Clock

- > Internal 1-32mhz high precision HIRC with support for calibration (error  $\pm 1\%$ )

- $\triangleright$  Internal 64KHz low-speed LIRC, calibration supported (error  $\pm 1\%$ )

> External 32.768 KHz low speed crystal, need external capacitor

### Reset

- > Power on reset

- > Undervoltage reset

- > Reduction foot reduction

- > Watchdog overflow reset

### • GPIO

- ➤ Up to 14 GPIos

- ► All ports can input and output 5V signals

- ➤ All support rising edge/falling edge/double edge interrupts

- ➤ All support wakeup function

- > There are full drive and small drive two gears.

- > Support OD output low mode.

- ightharpoonup Supports independent control of pull-down resistor, 30K $\Omega$  resistance

### LVD low voltage detection reset

Provides 4 levels of low voltage detection voltage (1.8/2.0V, 2.1/2.3V, 2.4/2.6V, 3.4/3.6V)

### Digital peripherals

- > 1 SPI high-speed serial interface, supporting master-slave mode

- > 1 I2C interface, support multiple master and slave mode (only TX8C1011 series support)

- > 2 UART ports with up to 4Mbps support

### • Timer resources

> 2 16-bit advanced timers, can support 2 pairs of complementary outputs or 4 independent PWM outputs (same cycle, independent duty cycle

- configuration), support dead zone insertion and event braking function, support single pulse mode

- ▶ 1 16-bit general timer, both support Capture, Count, PWM function

- > 28-bit universal timers (can be combined into 116-bit universal Timer, both support Capture, Count, PWM functions), can support infrared send and receive functions (requires two timers)

- > 1 watchdog timer

### High security

> 16 bit CRC validation is supported to ensure data accuracy

### • Low power consumption

- Support Idle, Stop, Sleep low power mode

- > Static power consumption 3uA @25 ° C

- ➤ Low power wake-up time is less than 100us

### • 1 high precision 12-bit analog-to-digital converter (ADC)

- The fastest conversion clock supports 4MHz and the fastest speed is 200Ksps

- > Offset correction step 2mV, DNL +-2 INL +-4

- There are 13 external input channels and 2 analog channels

- The effective bit of ADC is about 10bit (5V voltage regulator is supplied, and the ADC is connected to the VCC of the chip through the internal switch. This voltage is used as the reference voltage of the ADC, and the full scale of the ADC is equal to VCC).

### • 2 analog comparators (ACmps)

- ➤ 2 low misaligned comparators with correction step 1mV

- > The comparator supports 120 divider gears for negative input of

precision BG or VDDADC

- ➤ Both comparators support rail-to-rail input mode, and the positive and negative sides support 2 GPIOs each

- > Dry suction protection is supported

- > Supports short circuit protection

### • High reliability

- ➤ ESD HBM 8KV

- > Latch-up ±200mA @25°C

- 96-bit chip Unique ID (UID)

- Packaging

- ➤ Die Form

- > SOP8/MSOP10/SOP14/SOP16/QFN16

- Operating temperature range

- > -40°C <sup>~</sup> 85°C

# 2. Central processing unit

TX8C101x is fully compatible with the traditional 8051 microcontroller. All mnemonic and binary codes of instructions are compatible with the 8051. The TX8C101x processor uses some architecture optimizations to expand the SP, DPTR and other commonly used registers. Compared with the traditional 8051, the performance has been greatly improved.

The ALU in TX8C101x can realize various 8-bit operations with ACC (0xE0), B

(0xF0), PSW (0xD0) registers.

The ALU can perform typical operations as follows:

- Basic arithmetic operations: addition, subtraction, multiplication, division

- Other arithmetic operations: self-addition, self-subtraction, BCD adjustment, comparison

- Logical operations: AND, OR, XOR, negation, shift

- Boolean bit operations: set, zero, negate, jump by bit judgment, carry operation

# 2.1. Accumulator (ACC)

The ALU is an 8Bit wide arithmetic logic unit. All the mathematical and logical operations of the MCU are completed through it. It can add, subtract, shift data and logic operations; The ALU also controls the status bit (in PSW status register), which is used to represent the status of the operation result.

The ACC register is an 8Bit register where the ALU's result can be stored.  $Addr = 0xE0 \ (SFR)$

| Bit(s) | Name | Description          | R/W | Reset |

|--------|------|----------------------|-----|-------|

| 7:0    | ACC  | Accumulator register | RW  | 0x0   |

# 2.2. Register (B)

The B register is used when using multiplication and division instructions, the result of multiplication is 8bit higher, and the result of division is 8bit lower.

It can also be used as a general purpose register if multiplication and division instructions are not used.

Addr = 0xF0 (SFR)

| Bit(s) | Name | Description | R/W | Reset |

|--------|------|-------------|-----|-------|

| 7:0    | В    | B register  | RW  | 0x0   |

# 2.3. Stack pointer register (SP)

The SP register points to the lower 8bit address of the stack, defaults to 0x07 after reset, and the value of this SP can be modified. The operations that affect the SP are: instruction PUSH, LCALL, ACALL, POP, RET, RETI, as well as the entry interrupt.

Addr = 0x81 (SFR)

| Bit(s) | Name | Description            | R/W | Reset |

|--------|------|------------------------|-----|-------|

| 7:0    | SP   | Stack pointer register | RW  | 0x7   |

# 2.4. Stack Pointer register (SPH)

The SPH register points to the stack high 8bit address, the significant bit 1bit, and the default bit 0x0 after reset, which in combination with the SP means that the area of the stack starts at 0x07 of the RAM address. This value can be modified, if the stack area is set to start at 0x0B, the values of SPH and SP will be set to 0x0 and 0x0A respectively after reset.

The operations that affect SPH are: instructions PUSH, LCALL, ACALL, POP, RET, RETI as well as the entry interrupt.

Addr = 0x9B (SFR)

| Bit(s) Name Description | R/W | Reset |  |

|-------------------------|-----|-------|--|

|-------------------------|-----|-------|--|

| 7:1 | _   | -                               | -  | =   |

|-----|-----|---------------------------------|----|-----|

| 0   | SPH | Stack pointer register high bit | RW | 0x0 |

# 2.5. Data pointer register (DPTRO/DPTR1)

Data pointer is mainly used in MOVX, MOVC instructions, its role is to locate the address of RAM and ROM. There are two data pointer registers DPTRO and DPTR1 inside the chip, which are selected through the DPSEL register.

Each set of Pointers includes two 8-bit registers: DPTRO={DPHO, DPLO} and DPTR1={DPH1, DPL1}.

Addr = 0x82 (SFR)

| Bit(s) | Name | Description                                  | R/W | Reset |

|--------|------|----------------------------------------------|-----|-------|

| 7:0    | DPL0 | DPTRO data pointer register eight bits lower | RW  | 0x0   |

Addr = 0x83 (SFR)

| Bit(s) | Name | Description                                 | R/W | Reset |

|--------|------|---------------------------------------------|-----|-------|

| 7:0    | DPH0 | DPTRO data pointer register eight bits high | RW  | 0x0   |

Addr = 0x84 (SFR)

| Bit(s) | Name | Description                                  | R/W | Reset |

|--------|------|----------------------------------------------|-----|-------|

| 7:0    | DPL1 | DPTR1 data pointer register eight bits lower | RW  | 0x0   |

Addr = 0x85 (SFR)

| Bit(s) | Name  | Description                              | R/W     | Reset |

|--------|-------|------------------------------------------|---------|-------|

| 7.0    | DDI 1 | The DPTR1 data pointer register is eight | <b></b> |       |

| 7:0    | DPL1  | bits high                                | RW      | 0x0   |

# 2.6. Data Pointer Control Register (DPCFG)

Addr = 0x86 (SFR)

| Bit(s) | Name    | Description                                                                                                                                                                                                      | R/W | Reset      |

|--------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------------|

| 7:6    | Name IA | <pre>Interrupt start address and add way select bits IA[0] 0x0: Interrupt address = (interrupt vector *8) +3 0x1: Interrupt address = (interrupt vector +1) *3 IA[1] 0x0: Interrupt start address is 0x300</pre> | R/W | Reset  0x2 |

| 5      | DPID0   | Ox1: Interrupt start address is 0x8000  DPTRO plus 1/ minus 1  Ox0: Add 1 to DPTRO  Ox1: DPTRO minus 1                                                                                                           | RW  | 0x0        |

| 4      | DPID1   | DPTR1 add 1/ subtract 1  0x0: DPTR1 plus 1  0x1: DPTR1 minus 1                                                                                                                                                   | RW  | 0x0        |

| 3      | DPAID   | DPTRO/DPTR1 self-add and self-subtract enable bits  0x0: Off 0x1: Open                                                                                                                                           | RW  | 0x0        |

| 2      | DPTSL   | DPSEL automatically flips the enable bit 0x0: Off 0x1: Open                                                                                                                                                      | RW  | 0x0        |

| 1      | 7.      | -                                                                                                                                                                                                                | _   | _          |

| 0      | DPSEL   | Select the DPTRO /DPTR1 bits  0x0: DPTR0 is valid  0x1: DPTR1 is valid                                                                                                                                           | RW  | 0x0        |

# 2.7. Program Status register (PSW)

Addr = 0xD0 (SFR)

| Bit(s) | Name     | Description                                                                                                                       | R/W | Reset |

|--------|----------|-----------------------------------------------------------------------------------------------------------------------------------|-----|-------|

| 7      | СУ       | Carry flag bit 0x0: No carry bit 0x1: Carry free                                                                                  | RW  | 0x0   |

| 6      | AC       | Auxiliary carry flag bit 0x0: No carry bit 0x1: Carry free                                                                        | RW  | 0x0   |

| 5      | F0       | Universal flag bit 0                                                                                                              | RW  | 0x0   |

| 4:3    | RS1, RS0 | Register set select bit  0x0: Register group 0  0x1: Register group 1  0x2: Register group 2  0x3: Register group 3               | RW  | 0x0   |

| 2      | OV       | Overflow flag bit  0x0: No overflow for arithmetic or logical operations  0x1: An arithmetic or logical operation has an overflow | RW  | 0x0   |

| 1      | F1       | Generic flag bit 1                                                                                                                | RW  | 0x0   |

| 0      | P        | The parity flag bit  0x0:1 is even in ACC  0x1:1 is odd in ACC                                                                    | RW  | 0x0   |

# 2.8. Program counter (PC)

The program counter (PC) controls the instruction execution order in the program memory FLASH. It can address the whole range of FLASH. After getting the instruction

code, the program counter (PC) will automatically add one to point to the address of the next instruction code. However, when executing jump, conditional jump, assignment to PCL, subprogram call, initialized reset, interrupt, interrupt return, subprogram return and other operations, the PC will load the address related to the instruction instead of the address of the next instruction.

When a conditional jump instruction is encountered and the jump condition is met, the next instruction read during the execution of the current instruction will be discarded, and a null instruction operation cycle will be inserted, and then the correct instruction can be obtained. Otherwise, the next instruction will be executed sequentially.

# 3. Memory

TX8C101x has three kinds of internal memory: IDATA, XDATA, program memory.

Program memory can only read not write, the size of the program memory is 4K bytes. XDATA is 1K bytes in size (with 512 bytes for XSFR) and 256 bytes for IDATA.

# 3.1. Program memory

The program pointer of TX8C101x is 16 bits, and the maximum addressable space of TX8C101X is 64K bytes. In fact, only 4K bytes of program storage space are realized.

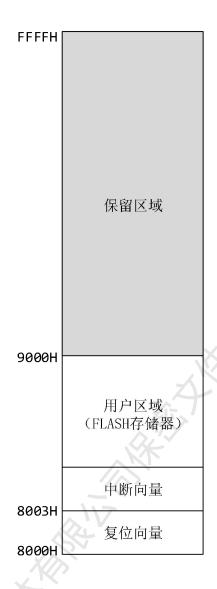

Figure 3-1 program storage space

After the reset, the MCU executes from 0x8000. Starting from 0x8003 is the interrupt vector table. When an interrupt occurs and the interrupt is enabled, the PC will jump to the corresponding interrupt vector position to execute.

## 3. 2. XDATA

XDATA has 256 bytes and addresses 0x300 to 0x3FF and can be used for data storage.

# 3. 3. IDATA

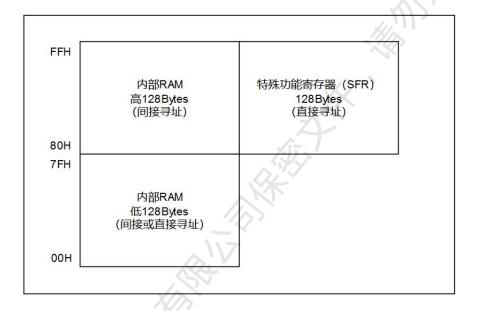

The size of the internal data memory space is 256 bytes.

The lower 128 bytes of the address space of the internal data memory can be accessed by byte, and the upper 128 bytes and the SFR share the same address space. Direct access to the upper 128 bytes will access the SFR space, and the upper 128 bytes can only be accessed by indirect addressing.

Figure 3.2 The data store

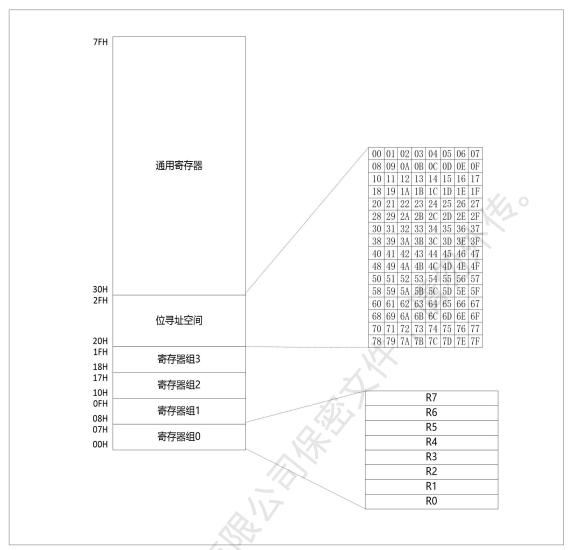

Figure 3.3 Internal low 128 bytes data space allocation

# 3.4. SFR space

|     | 0Н/8Н        | 1Н/9Н       | 2H/AH        | ЗН/ВН        | 4H/CH       | 5H/DH        | 6Н/ЕН          | 7H/FH        |

|-----|--------------|-------------|--------------|--------------|-------------|--------------|----------------|--------------|

| F8H | UARTO_BAUDO  | UARTO_BAUD1 | UARTO_DATA   | UART1_CON    | UART1_STA   | UART1_BAUDO  | UART1_BAUD1    | UART1_DATA   |

| F0H | В            | SPIO_CON    | SPIO_BAUD    | SPIO_DAT     | SPIO_STA    | STMR_ALLCON  | UARTO_CON      | UARTO_STA    |

| Е8Н | STMR2_BRAKE  | STMR2_DTR   | STMR2_PCONRA | STMR2_PCONRB | STMR2_IE    | STMR2_SR     | ADK_CFG3       | -            |

| ЕОН | ACC          | STMR2_CMPAH | STMR2_CMPBL  | STMR2_CMPBH  | STMR2_CR    | STMR2_FCONR  | STMR2_VPERR    | STMR2_DTUA   |

| D8H | STMR1_PCONRB | STMR1_IE    | STMR1_SR     | STMR2_CNTL   | STMR2_CNTH  | STMR2_PRL    | STMR2_PRH      | STMR2_CMPAL  |

| DOH | PSW          | STMR1_CR    | STMR1_FCONR  | STMR1_VPERR  | STMR1_DTUA  | STMR1_BRAKE  | STMR1_DTR      | STMR1_PCONRA |

| С8Н | STMR1_CNTL   | STMR1_CNTH  | STMR1_PRL    | STMR1_PRH    | STMR1_CMPAL | STMR1_CMPAH  | STMR1_CMPBL    | STMR1_CMPBH  |

| СОН | TMR2_CONL    | TMR2_CONH   | TMR2_CNTL    | TMR2_CNTH    | TMR2_PRL    | TMR2_PRH     | TMR2_PWML      | TMR2_PWMH    |

| В8Н | IPO          | IP1         | LVD_CONO     | LVD_CON1     | LVD_CON2    | LVD_CON3     | LP_CON         | SYS_PND      |

| ВОН | TMR1_CONL    | TMR1_CONH   | TMR1_CNTL    | TMR1_CNTH    | TMR1_PRL    | TMR1_PRH     | TMR1_PWML      | TMR1_PWMH    |

| А8Н | IE0          | IE1         | FLASH_TRIM   | WKUP_CONO    | WKUP_PND    | WDT_CON      | WDT_KEY        | -            |

| АОН | FLASH_CON    | FLASH_STA   | FLASH_DATA   | FLASH_TIMO   | FLASH_TIM1  | FLASH_CRCLEN | FLASH_PASSWORD | FLASH_ADDR   |

| 98H | ADK_CHS0     | ADK_CHS1    | ADK_CFG2     | SPH          | PCON1       | ADK_CON      | CRC_REG        | CRC_FIF0     |

| 90Н | P1           | ADC_CFG0    | ADC_CFG1     | ADC_STA      | ADC_DATAHO  | ADC_DATALO   | ADC_DATAH1     | ADC_DATAL1   |

| 88H | TMRO_CONL    | TMRO_CONH   | TMRO_CNTL    | TMRO_CNTH    | TMRO_PRL    | TMRO_PRH     | TMRO_PWML      | TMRO_PWMH    |

| 80Н | PO           | SP          | DPLO         | DPH0         | DPL1        | DPH1         | DPS            | PCONO        |

# 4. System clock

# 4.1. Clock System Overview

The system chip has a 32MHz high speed and high precision RC oscillator, and an external 32.768KHz low speed crystal oscillator, as well as a 64KHz low speed RC oscillator integrated in the internal PMU.

# 4.2. Clock system main functions

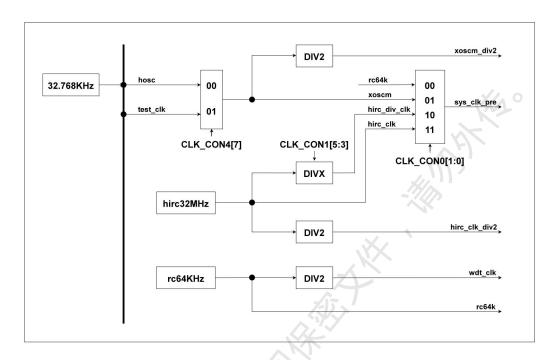

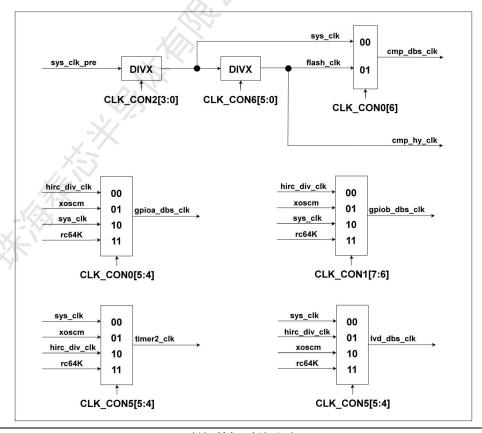

The clock source of TX8C101x chip comes from three different clocks, which are the off-chip low speed crystal of 32.768KHz, the on-chip low speed RC of 64K and the on-chip high speed RC of 32M. As shown in Figure 4-1, the system clock can be selected from the above three clock sources by CLK\_CONO[1:0], and the selected clock is the fastest clock (hereinafter referred to as sys\_clk\_pre). As shown in Figure 4-2, sys\_clk\_pre is divided by CLK\_CON2[3:0], and the clock after frequency division is the system clock (hereinafter referred to as sys\_clk). sys\_clk is used by most peripherals and analog-to-digital mixing modules in the system. For example, UART, SPI, CRC16 and other peripherals all use sys\_clk. As shown in Figure 4-2, the filter clock of GPIO port, the clock of Timer2 module and the low power detection are special modules that use sys\_clk, the off-chip low speed crystal of 32.768KHz, the on-chip low speed RC of 64K, and the on-chip high speed RC of 32M after frequency division clock to select.

# 4.3. Block diagram of the clock system

Figure 4-1 block diagram of the system clock

# 4.4. System oscillator

### 4.4.1. Internal low speed RC oscillator

PMU is integrated with a 64KHz normally open low speed RC oscillator, when the chip is powered on, the system works at the 64KHz clock, complete the power-on reset process, until the system reset to release the program.

# 4.4.2. Internal high-speed RC oscillator

An on-chip high-speed RC oscillator is integrated inside the chip, which supports the output clock of up to 32MHz for the system. It is turned off by default. Users need to configure the system register AIP\_CONO[7]=1 to turn on the high-speed RC oscillator in the program, and can also turn off the clock source by configuing AIP\_CONO[7]=0. Note that the system needs to switch to the low speed RC oscillator before turning off the clock. The high speed RC oscillator can be calibrated by a calibration procedure during mass production to ensure its accuracy meets the requirements of the application scenario.

### 4.4.3. External low-speed crystal oscillator

A crystal oscillator starter circuit is integrated inside the chip, which can be connected to a low speed 32.768KHz passive crystal oscillator as the working clock source of the system. If it is off by default, the clock source can be turned on by configuing the system register AIP\_CON1[3]=1; It can also be turned off by configuring AIP\_CON1[3]=0.

# 5. Reset the system

### 5.1. Power-on reset

Power on chip POR reset.

# 5.2. Power down reset power down

BOR reset for chip power failure.

# 5.3. Watchdog reset

The chip has a watchdog module that runs independently of the system and is used to protect the system from resetting and restarting after an exception has occurred. The working clock of the watchdog module is a 64KHz low-speed RC 2 division clock, which is independent of the system clock and operates at 32KHz. The default configuration is to reset the system every 2 seconds. So the user program needs to feed the dog before the watchdog resets, so that it can be retimed. The user can configure the watchdog reset time interval from 8ms to 262s, and can choose the watchdog to generate an interrupt, no longer. You can choose between interrupt and reset.

# 5.3.1. Control the register list

Table 5-1 List of WDT registers

| Address    | Register Name | Description      |

|------------|---------------|------------------|

| OxAD (SFR) | WDT_CON       | WDT_CON register |

| OxAE (SFR) | WDT_KEY       | WDT_KEY register |

# 5.3.2. Register details

5. 3. 2. 1. WDT\_CON

Addr = OxAD (SFR)

| Bit(s) | Name   | Description                                | R/W | Reset |

|--------|--------|--------------------------------------------|-----|-------|

|        |        | WDT wakeup feature enable bit              |     |       |

|        |        | Write WDT_KEY=OxEE, set                    |     |       |

| 7      | WAKEEN | Write WDT_KEY=0x22, reset                  | RO  | 0x0   |

|        | . <    | 0x0: Close                                 |     |       |

|        |        | 0x1: Open                                  |     |       |

|        | WDTPND | The WDT counter is full of marker bits     |     |       |

| C      |        | Write WDT_KEY=OxAA to clear the marker bit | DO. | 0x0   |

| 6      |        | 0x0: The counter is not full               | RO  |       |

|        |        | 0x1: The counter is full                   |     |       |

|        | ÀI.    | WDT interrupt function enable bit          |     |       |

|        | INTEN  | Write WDT_KEY=0x5A, set                    |     |       |

| 5      |        | Write WDT_KEY=0xA5, reset                  | RO  | 0x0   |

|        |        | 0x1: Turn on interrupt function            |     |       |

|        |        | 0x0: Enable reset functionality            |     |       |

| 4      | WDTE   | WDT enable bit                             | RW  | 0x1   |

|     |      | Write WDT_KEY=0xCC, set                  |      |     |

|-----|------|------------------------------------------|------|-----|

|     |      | Write WDT_KEY=0xDD, reset                |      |     |

|     |      | 0x0: Disable watchdog function           |      |     |

|     |      | 0x1: Turn on the watchdog function       |      |     |

|     |      | Pre-division coefficient                 |      |     |

|     |      | You must write WDT_KEY=0x55 before       |      |     |

|     |      | configuring this bit field each time     | ./   |     |

|     |      | 0x0: Regardless of frequency             | XXT. |     |

|     |      | 0x1:2 frequency division                 |      |     |

|     |      | 0x2:4 split frequency                    |      |     |

|     |      | 0x3:8 frequency division                 |      |     |

|     |      | 0x4:16 split frequency                   |      |     |

|     |      | 0x5:32 split frequency                   |      |     |

|     |      | 0x6:64 split frequency                   |      |     |

| 3:0 | PSR  | 0x7:128 split frequency                  | RW   | 0x8 |

|     |      | 0x8:256 split frequency                  |      |     |

|     |      | 0x9:512 split frequency                  |      |     |

|     |      | 0xA: 1024 frequency division             |      |     |

|     |      | 0xB: 2048 split frequency                |      |     |

|     |      | OxC: 4096 split frequency                |      |     |

|     |      | OxD: 8192 split frequency                |      |     |

|     |      | OxE: 16384 divider                       |      |     |

|     |      | 0xF: 32768 split frequency               |      |     |

|     | -3// | Watchdog reset time =1/32K*256* division |      |     |

|     | 1/-/ | factor                                   |      |     |

# 5. 3. 2. 2. WDT\_KEY

Addr = OxAE (SFR)

| Bit(s | ) Name   | Description | R/W  | Reset |

|-------|----------|-------------|------|-------|

| DIL(S | /   Name | Description | IX/W | neset |

|     |         | Feed the dog data register                     |       |     |

|-----|---------|------------------------------------------------|-------|-----|

|     |         | The software must write OxAA at regular        |       |     |

|     |         | intervals to complete the dog-feeding          |       |     |

|     |         | operation, otherwise, the watchdog will        |       |     |

|     |         | generate a reset when the counter is zero      |       |     |

|     |         | When pending is 1, write OxAA to clear pending |       |     |

|     |         | 0x55: Indicates that wdt_psr is allowed to be  | .// 0 |     |

| 7:0 | WDT_KEY | accessed and set                               | WO    | 0x0 |

|     |         | OxDD: Turn off the watchdog                    |       |     |

|     |         | OxCC: Start watchdog work                      | 1     |     |

|     |         | OxAA: Feed the dog and clear wdt_pending       |       |     |

|     |         | OxA5: Interrupt is closed                      |       |     |

|     |         | Ox5A: Enable interrupt                         |       |     |

|     |         | 0x22: Turn off wake up                         |       |     |

|     |         | OxEE: Turn wake up on                          |       |     |

# 5.4. Low power detection reset

PMU internal integrated low voltage detection and over current detection function circuit, used to detect PMU power supply part of the abnormal situation, and can detect the low voltage and over current and other abnormal situation through the interrupt report to the CPU for system exception handling program. In addition, the low voltage abnormal signal can generate a reset signal to reset the system, so as to avoid the circuit working abnormally under low voltage conditions and cause the user program to run. The threshold for low voltage detection can be set through the LVD control register. The LVD control register can be set to filter and dejitter the abnormal signal, to avoid the normal power supply voltage drop caused by the transient change of the system and the occurrence of accidental low power reset system.

# 5.4.1. Control register list

Table 5-2 List of LVD registers

| Address    | Register Name | Description       |

|------------|---------------|-------------------|

| OxBA (SFR) | LVD_CONO      | LVD_CONO register |

| 0xBB (SFR) | LVD_CON1      | LVD_CON1 register |

| 0xBC (SFR) | LVD_CON2      | LVD_CON2 register |

| 0xBD (SFR) | LVD_CON3      | LVD_CON3 register |

# 5.4.2. Register details

# 5. 4. 2. 1. LVD\_CONO

Addr = OxBA (SFR)

| Bit(s) | Name        | Description                                                                                                                                          | R/W | Reset |

|--------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|

| 7      | _           | \X                                                                                                                                                   | 1   | -     |

| 6      | LVDOE       | LVD interrupt and reset functions output to the system enable bit  To use all LVD related functions, LVDOE must be set to bit 1  0x0: Off  0x1: Open | RW  | 0x1   |

| 5      | LVDVDDRSTEN | LVD VDD low voltage reset function enable bit $0x0$ : Off $0x1$ : Open                                                                               | RW  | 0x1   |

| 4      | LVDVCCRSTEN | LVD VCC low voltage reset function enable bit $0x0$ : Off $0x1$ : Open                                                                               | RW  | 0x1   |

|     |              | VCC power supply voltage low voltage detection threshold set |      |                  |

|-----|--------------|--------------------------------------------------------------|------|------------------|

|     |              | 0x0:1.8/2.0V (power on threshold/power off                   |      |                  |

|     |              | threshold)                                                   |      |                  |

| 3:2 | PMULVD5SET   | 0x1:2.1/2.3V (power-up threshold/powerdown                   | RW   | 0x0              |

| 0.2 | 1 MOLVDOOL1  | threshold)                                                   | I(II | UAU              |

|     |              | 0x2:2.4/2.6V (power-up threshold/powerdown                   | // 0 |                  |

|     |              | threshold)                                                   | KYT  |                  |

|     |              | 0x3:3.4/3.6V (power-up threshold/powerdown                   | 7    |                  |

|     |              | threshold)                                                   |      |                  |

|     |              | 1.5V digital logic system operating voltage                  |      |                  |

| 1   | DMIII VD15EN | VDD low current detection function enable bit                | DW   | 0 <sub>w</sub> 1 |

|     | PMULVD15EN   | 0x0: Off                                                     | RW   | 0x1              |

|     |              | 0x1: Open                                                    |      |                  |

|     |              | VCC power supply VCC voltage low voltage                     |      |                  |

| 0   | PMULVD5EN    | detection function enable bit                                | RW   | 0x1              |

|     |              | 0x0: Off                                                     | I\W  | UXI              |

|     |              | 0x1: Open                                                    |      |                  |

# 5. 4. 2. 2. LVD\_CON1 Addr = 0xBB (SFR)

| Bit(s) | Name      | Description                                                                                                           | R/W | Reset |

|--------|-----------|-----------------------------------------------------------------------------------------------------------------------|-----|-------|

| 7      | - 15      | 1                                                                                                                     | ı   | -     |

| 6      | VDDOCPND  | VDD overcurrent detection marker bit Write 1 Clear the marker bit 0x0: VDD is not overflowing 0x1: VDD is overflowing | RW  | 0x0   |

| 5      | LVDVDDPND | VDD low current detection marker bit Write 1 Clear the marker bit 0x0: VDD has no low power 0x1: VDD is low           | RW  | 0x0   |

| 4 | LVDVCCPND    | VCC low current detection marker bit Write 1 Clear the marker bit 0x0: VCC has no low power 0x1: VCC low power | RW | 0x0 |

|---|--------------|----------------------------------------------------------------------------------------------------------------|----|-----|

| 3 | LVDVCCSYNDIS | LVD VCC low current detects synchronizer off bit 0x0: Turn on the synchronizer 0x1: Turn off the synchronizer  | RW | 0x1 |

| 2 | VDDOCBPSEN   | VDD overcurrent filter dejitter function off bit 0x0: Turn on filter 0x1: Turn off the filter                  | RW | 0x1 |

| 1 | LVDVDDBPSEN  | VDD low electrical filter dejitter function off bit  0x0: Turn on filter  0x1: Turn off the filter             | RW | 0x1 |

| 0 | LVDVCCBPSEN  | VCC Low electrical filter dejitter function off bit  0x0: Turn on filter  0x1: Turn off the filter             | RW | 0x1 |

# 5. 4. 2. 3. LVD\_CON2

Addr = 0xBC (SFR)

| Bit(s) | Name    | Description                                                                                                                                                                                                                          | R/W | Reset |

|--------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|

| 7      | -15-3   | _                                                                                                                                                                                                                                    |     | _     |

| 6:0    | DBSHLMT | LVD low current and overcurrent anomaly detection filter high level filter clock cycle set number  Note: The LVD filter clock can be selected through the system configuration register CLKCON5[3:2]. The user can choose the filter | RW  | 0x2   |

function according to the use scenario. The

delay time will be determined by the set

filter clock period and the number of

configured filter high level and low level

filter cycles. The longer the filter clock

period is set, the more the number of filter

cycles will lead to a longer delay. The user

can configure the delay reasonably according

to the tolerance of the delay. In some delay

sensitive application scenarios, the filter

function can be turned off.

#### 5. 4. 2. 4. LVD\_CON3

Addr = OxBD (SFR)

| Bit(s) | Name    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | R/W | Reset |

|--------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|

| 7      | _       | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | _   | ı     |

| 6:0    | DBSLLMT | LVD low current and overcurrent anomaly detection filter low level filter clock cycle set number  Note: The LVD filter clock can be selected through the system configuration register CLKCON5[3:2]. The user can choose the filter function according to the use scenario. The delay time will be determined by the set filter clock period and the number of configured filter high level and low level filter cycles. The longer the filter clock period is set, the more the number of filter cycles will lead to a longer delay. The user can configure the delay reasonably according to the tolerance of the delay. In some delay sensitive application scenarios, the filter | RW  | 0x2   |

function can be turned off.

#### 6. Low power management

The TX8C101x chip system supports three low power modes with different power levels, from high to low: Idle Mode, Stop Mode and Sleep Mode. The lowest power consumption is Sleep low power mode, in which the leakage of the whole chip can be about 3uA at normal temperature.

#### 6.1. Idle Mode and wakeup

Enter Idle Mode by configuring the system register LP\_CON[7]=1. In Idle mode only the CPU work clock is turned off and the CPU stops working. After waking up the Idle Mode, the interrupt service subroutine of the current wakeup Idle Mode will be entered and executed.

### 6.2. Stop Mode and wake up

Enter Stop Mode by configuring the system register LP\_CON[1]= 1. In Stop mode, the system clock is turned off, and the CPU and most peripherals in the system clock domain stop working. Stop Mode is woken by selecting a variety of wake-up sources, including: all GPIOs, comparators, basic Timer2, watchdog, LVDVCC (Low voltage detection signal for the power supply). After Stop Mode wakes up, it will continue to run the following user program.

#### 6.3. Sleep Mode and wake up

Enter the lowest power consumption Sleep Mode by configuring the system register LP\_CON[0]=1. In Sleep mode, the system clock is turned off, the CPU and most of the system clock domain peripherals stop working, in addition to the PMU other analog modules should be turned off, but XOSC can choose to turn on/off. By selecting a variety of awaken to awaken the Sleep Mode source, wake up the source including: all GPIO level transformation sensei, basic Timer2 timer interrupt sensei, watchdog reset. After Sleep Mode is awakened, the following user program will continue to run through the LP\_CON[6]=1 configured before entering Sleep mode. If LP\_CON[6]=0, the system will be reset to run the user program again.

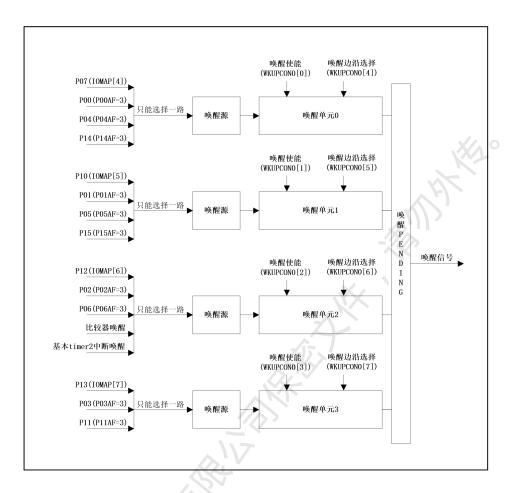

### 6.4. Low power consumption awakens the unit structure

Figure 6-1 wake structure with low consumption

### 6.5. Register details

#### 6. 5. 1. WAUP CONO

Addr = 0 xab (SFR)

| Bit(s) | Name       | Description                                   | R/W | Reset |

|--------|------------|-----------------------------------------------|-----|-------|

|        | \$1        | Low power mode wakeup channel 3 input trigger |     |       |

|        | WKUP3EDG   | level setting                                 | DW  | 0x0   |

| 7      |            | 0x0: High level triggers wakeup               | RW  |       |

|        |            | Ox1: Low level triggers wakeup                |     |       |

|        | WWW.DODD.G | Low power mode wakeup channel 2 input trigger | DW  |       |

| 6      | WKUP2EDG   | level setting                                 | RW  | 0x0   |

|   |              | OxO: High level triggers wakeup               |       |     |

|---|--------------|-----------------------------------------------|-------|-----|

|   |              | Ox1: Low level triggers wakeup                |       |     |